**CONTROLLER MANUAL**

# FR30 32-Bit Microcontroller MB91F109 Hardware Manual

# FR30 32-Bit Microcontroller MB91F109 Hardware Manual

## **PREFACE**

#### **■** Objectives and Intended Reader

The MB91F109 has been developed as one of the "32-bit single-chip microcontroller FR30 series" products that use new RISC architecture CPUs as their cores. It has optimal specifications for embedding applications that require high CPU processing power.

This manual explains the functions and operations of the MB91F109 for the engineers who actually develop products using the MB91F109. Read this manual thoroughly. Refer to the instruction manual for details on individual instructions.

#### **■** Trademarks

FR stands for FUJITSU RISC controller, a product of Fujitsu Limited.

Embedded Algorithm<sup>TM</sup> is a trademark of Advanced Micro Devices, Inc.

#### ■ Organization of This Manual

This manual consists of 16 chapters and an appendix.

#### **Chapter 1 Overview**

Chapter 1 provides basic general information on the MB91F109, including its characteristics, a block diagram, and function overview.

#### Chapter 2 CPU

Chapter 2 provides basic information on the FR series CPU core functions including the architecture, specifications, and instructions.

#### **Chapter 3 Clock Generator and Controller**

Chapter 3 provides detailed information on the generation and control of the clock that controls the MB91F109.

#### Chapter 4 Bus Interface

Chapter 4 explains the basic items of the external bus interface, register configuration and functions, bus operations, bus timing, and provides bus operation program samples.

#### Chapter 5 I/O Ports

Chapter 5 provides an overview of I/O ports, explains the I/O port register configuration and the conditions for using external terminals as I/O ports.

#### Chapter 6 External Interrupt/NMI Controller

Chapter 6 provides an overview of the external interrupt/NMI controller, explains the register configuration and functions, and operations of the external interrupt/NMI controller.

#### **Chapter 7 Delayed Interrupt Module**

Chapter 7 provides an overview of the delayed interrupt module, explains the register configuration and functions, and operations of the delayed interrupt module.

#### **Chapter 8 Interrupt Controller**

Chapter 8 provides an overview of the interrupt controller, explains the register configuration and functions, and operations of the interrupt controller. The chapter also explains the hold request cancel request function using examples.

#### Chapter 9 U-TIMER

Chapter 9 provides an overview of the U-TIMER, explains the register configuration and functions, and operations of the U-TIMER.

#### Chapter 10 UART

Chapter 10 provides an overview of the UART, explains the register configuration and functions, and operations of the UART.

#### Chapter 11 A/D Converter (Successive Approximation Type)

Chapter 11 provides an overview of the A/D converter, explains the register configuration and functions, and operations of the A/D converter.

#### Chapter 12 16-bit Reload Timer

Chapter 12 provides an overview of the 16-bit reload timer, explains the register configuration and functions, and operations of the 16-bit reload timer.

#### Chapter 13 Bit Search Module

Chapter 13 provides an overview of the bit search module, explains the register configuration and functions, and operations and save/restore processing of the bit search module.

#### **Chapter 14 PWM Timer**

Chapter 14 provides an overview of the PWM timer, explains the register configuration and functions, and operations of the PWM timer.

#### Chapter 15 DMAC

Chapter 15 provides an overview of the DMAC, explains the register configuration and functions, and operations of the DMAC.

#### **Chapter 16 Flash Memory**

Chapter 16 explains the flash memory functions and operations.

The chapter provides information on using the flash memory from the FR CPU.

For information on using the flash memory from the ROM writer, refer to the user's guide for the ROM writer.

#### **Appendix**

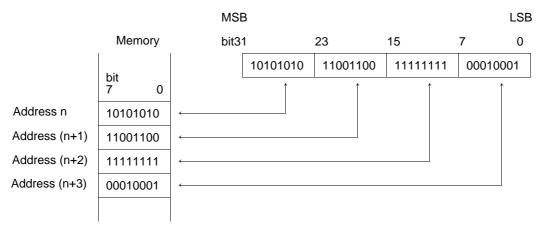

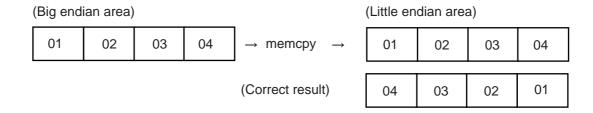

The appendix provides information on I/O maps, interrupt vectors, terminal states in each CPU status, notes on using the little endian area, and a listing of instructions. It includes details of these types of information that are not covered by the text that can be referenced for programming.

- 1. The contents of this document are subject to change without notice. Customers are advised to consult with FUJITSU sales representatives before ordering.

- 2. The information and circuit diagrams in this document are presented as examples of semiconductor device applications, and are not intended to be incorporated in devices for actual use. Also, FUJITSU is unable to assume responsibility for infringement of any patent rights or other rights of third parties arising from the use of this information or circuit diagrams.

- 3. The contents of this document may not be reproduced or copied without the permission of FUJITSU LIMITED.

- 4. FUJITSU semiconductor devices are intended for use in standard applications (computers, office automation and other office equipments, industrial, communications, and measurement equipments, personal or household devices, etc.).

#### **CAUTION:**

Customers considering the use of our products in special applications where failure or abnormal operation may directly affect human lives or cause physical injury or property damage, or where extremely high levels of reliability are demanded (such as aerospace systems, atomic energy controls, sea floor repeaters, vehicle operating controls, medical devices for life support, etc.) are requested to consult with FUJITSU sales representatives before such use. The company will not be responsible for damages arising from such use without prior approval.

- 5. Any semiconductor devices have inherently a certain rate of failure. You must protect against injury, damage or loss from such failures by incorporating safety design measures into your facility and equipment such as redundancy, fire protection, and prevention of over-current levels and other abnormal operating conditions.

- 6. If any products described in this document represent goods or technologies subject to certain restrictions on export under the Foreign Exchange and Foreign Trade Control Law of Japan, the prior authorization by Japanese government should be required for export of those products from Japan.

# **How to Read This Manual**

#### **■** Description Format of this Manual

Major terms used in this manual are explained below:

| Term   | Meaning                                                                                                                                                                                                                                                                                                                                                  |

|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| I-BUS  | 16-bit wide bus used for internal instructions. Since the FR series uses an internal Harvard architecture, independent buses are used for instructions and data. A bus converter is connected to the I-BUS.                                                                                                                                              |

| D-BUS  | Internal 32-bit wide data bus. Internal resources are connected to the D-BUS.                                                                                                                                                                                                                                                                            |

| C-BUS  | Internal multiplex bus. The C-BUS is connected to the I-BUS and D-BUS via a switch. An external interface module is connected to the C-BUS. Data and instructions are multiplexed in the external data bus.                                                                                                                                              |

| R-BUS  | Internal 16-bit wide data bus. The R-BUS is connected to the D-BUS via an adapter. Various I/O ports, the clock generator, and interrupt controller are connected to the R-BUS. Since the R-BUS is 16 bits wide in which addresses and data are multiplexed, it takes twice as much or more cycle time than usual for the CPU to access these resources. |

| E-unit | Operation executing unit                                                                                                                                                                                                                                                                                                                                 |

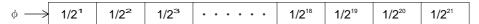

| ф      | System clock output from the clock generator to each internal resource connected to the R-BUS. The system clock at the highest speed shows the same cycle as source oscillation but is divided into 1, 1/2, 1/4, and 1/8 (or 1/2, 1/4, 1/8, and 1/16) by PCK1 and PCK0 of the clock generator GCR register.                                              |

| θ      | System clock or operation clock for the CPU and resources connected to a bus other than the R-BUS. The system clock at the highest speed shows the same cycle as source oscillation but is divided into 1, 1/2, 1/4, and 1/8 (or 1/2, 1/4, 1/8, and 1/16) by CCK1 and CCK0 of the clock generator GCR register.                                          |

# **CONTENTS**

| CHAP | PTER 1 OVERVIEW                                                         | 1  |

|------|-------------------------------------------------------------------------|----|

| 1.1  | MB91F109 Characteristics                                                | 2  |

| 1.2  | General Block Diagram of MB91F109                                       | 6  |

| 1.3  | Outside Dimensions                                                      | 7  |

| 1.4  | Pin Arrangement Diagrams                                                | 10 |

| 1.5  | Pin Functions                                                           | 14 |

| 1.6  | I/O Circuit Format                                                      | 22 |

| 1.7  | Memory Address Space                                                    |    |

| 1.8  | Handling of Devices                                                     | 26 |

| CHAP | PTER 2 CPU                                                              | 29 |

| 2.1  | CPU Architecture                                                        | 30 |

| 2.2  | Internal Architecture                                                   | 31 |

| 2.3  | Programming Model                                                       | 33 |

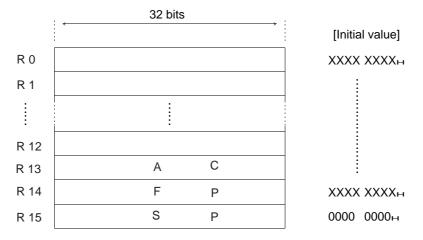

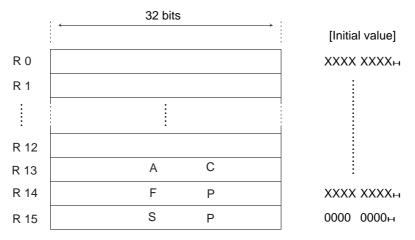

| 2.3  | 3.1 General-Purpose Registers                                           | 35 |

| 2.3  | 3.2 Special Registers                                                   | 36 |

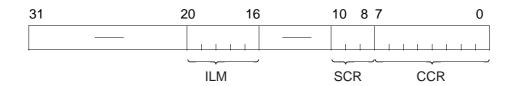

| 2.3  | 3.3 Program Status Register (PS)                                        | 39 |

| 2.4  | Data Structure                                                          |    |

| 2.5  | Word Alignment                                                          |    |

| 2.6  | Memory Map                                                              |    |

| 2.7  | Instruction Overview                                                    |    |

|      | 7.1 Branch Instructions with Delay Slots                                |    |

|      | 7.2 Branch Instructions without Delay Slots                             |    |

| 2.8  |                                                                         |    |

| 2.8  |                                                                         |    |

|      | 8.2 Interrupt Control Register (ICR)                                    |    |

|      | 8.3 System Stack Pointer (SSP)                                          |    |

|      | 8.4 Interrupt Stack                                                     |    |

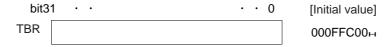

|      | 8.5 Table Base Register (TBR)                                           |    |

|      | 8.6 EIT Vector Table                                                    |    |

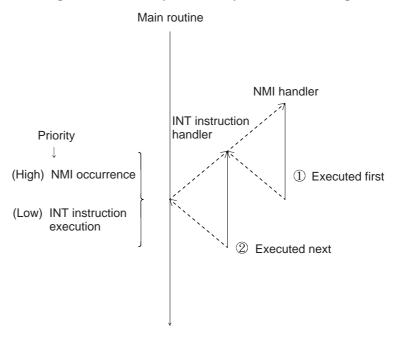

|      | 8.7 Multiple EIT Processing                                             |    |

|      | 8.8 EIT Operation                                                       |    |

| 2.9  | Reset Sequence                                                          |    |

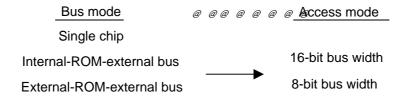

| 2.10 | Operation Mode                                                          | 69 |

| CHAP | PTER 3 CLOCK GENERATOR AND CONTROLLER                                   | 73 |

| 3.1  | Outline of Clock Generator and Controller                               |    |

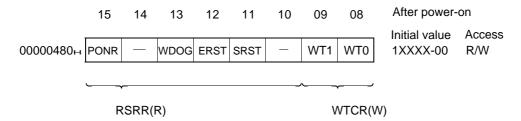

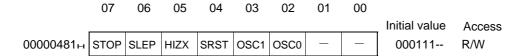

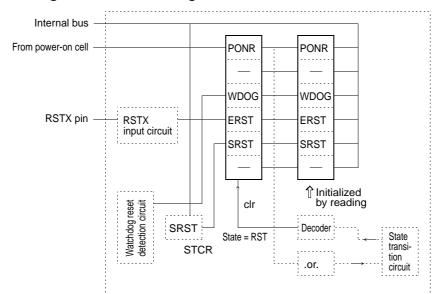

| 3.2  | Reset Reason Resister (RSRR) and Watchdog Cycle Control Register (WTCR) |    |

| 3.3  | Standby Control Register (STCR)                                         |    |

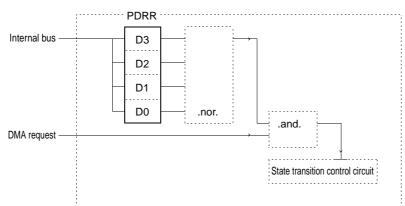

| 3.4  | DMA Request Suppression Register (PDRR)                                 |    |

| 3.5  | Timebase Timer Clear Register (CTBR)                                    |    |

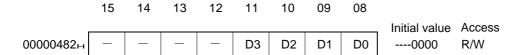

| 3.6  | Gear Control Register (GCR)                                             |    |

| 3.7  | Watchdog Timer Reset Delay Register (WPR)                               |    |

| 3.8  | PLL Control Register (PCTR)                                             | 86 |

|    | 3.9  | Gear Function                                            | . 87 |

|----|------|----------------------------------------------------------|------|

|    | 3.10 | Standby Mode (Low Power Consumption Mechanism)           | . 90 |

|    | 3.10 | .1 Stop State                                            | . 92 |

|    | 3.10 | .2 Sleep State                                           | . 95 |

|    | 3.10 | .3 Standby Mode State Transition                         | . 98 |

|    | 3.11 | Watchdog Function                                        | . 99 |

|    | 3.12 | Reset Source Hold Circuit                                | 101  |

|    | 3.13 | DMA Suppression                                          | 103  |

|    | 3.14 | Clock Doubler Function                                   | 105  |

|    | 3.15 | Example of PLL Clock Setting                             | 108  |

| Cŀ | HAPT | ER 4 BUS INTERFACE                                       | 111  |

|    | 4.1  | Outline of Bus Interface                                 | 112  |

|    | 4.2  | Chip Select Area                                         |      |

|    | 4.3  | Bus Interface                                            |      |

|    | 4.4  | Area Select Register (ASR) and Area Mask Register (AMR)  |      |

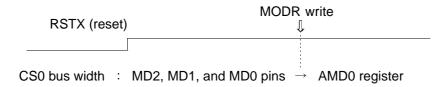

|    | 4.5  | Area Mode Register 0 (AMD0)                              |      |

|    | 4.6  | Area Mode Register 1 (AMD1)                              |      |

|    | 4.7  | Area Mode Register 32 (AMD32)                            |      |

|    | 4.8  | Area Mode Register 4 (AMD4)                              |      |

|    | 4.9  | Area Mode Register 5 (AMD5)                              |      |

|    | 4.10 | DRAM Control Register 4/5 (DMCR4/5)                      |      |

|    | 4.11 | Refresh Control Register (RFCR)                          |      |

|    | 4.12 | External Pin Control Register 0 (EPCR0)                  |      |

|    |      | External Pin Control Register 1 (EPCR1)                  |      |

|    |      | DRAM Signal Control Register (DSCR)                      |      |

|    |      | Little Endian Register (LER)                             |      |

|    |      | Relationship between Data Bus Widths and Control Signals |      |

|    |      | i.1 Bus Access with Big Endians                          |      |

|    |      | 3.2 Bus Access with Little Endians                       |      |

|    | 4.16 | 3.3 External Access                                      | 151  |

|    | 4.16 | .4 DRAM Relationships                                    | 155  |

|    | 4.17 | Bus Timing                                               | 159  |

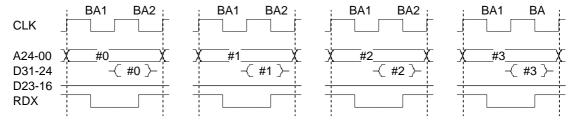

|    | 4.17 | 7.1 Basic Read Cycle                                     | 162  |

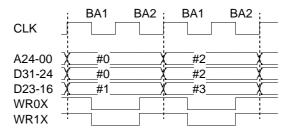

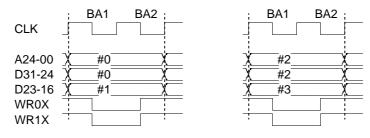

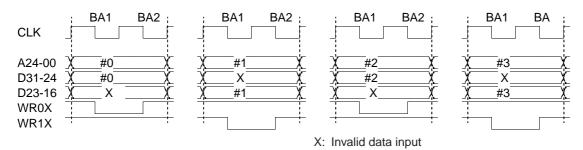

|    | 4.17 | 7.2 Basic Write Cycles                                   | 164  |

|    | 4.17 | 3 Read Cycles in Each Mode                               | 166  |

|    | 4.17 | 7.4 Write Cycles in Each Mode                            | 168  |

|    | 4.17 | 7.5 Read and Write Combination Cycles                    | 170  |

|    | 4.17 | '.6 Automatic Wait Cycles                                | 171  |

|    | 4.17 | 7.7 External Wait Cycles                                 | 172  |

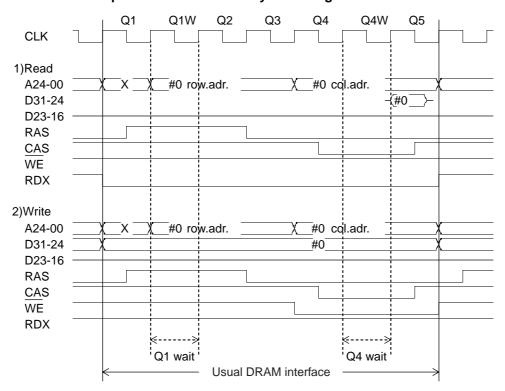

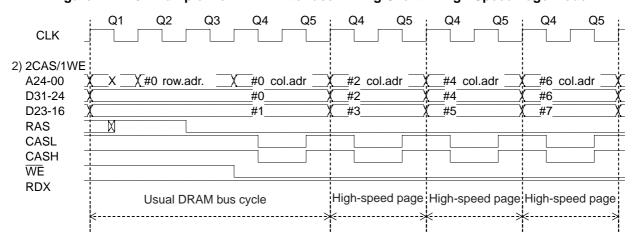

|    | 4.17 | '.8 Usual DRAM Interface: Read                           | 173  |

|    | 4.17 | '.9 Usual DRAM Interface: Write                          | 175  |

|    | 4.17 | 10 Usual DRAM Read Cycles                                | 177  |

|    | 4.17 | 111 Usual DRAM Write Cycles                              | 179  |

|    | 4.17 | '.12 Automatic Wait Cycles in Usual DRAM Interface       | 181  |

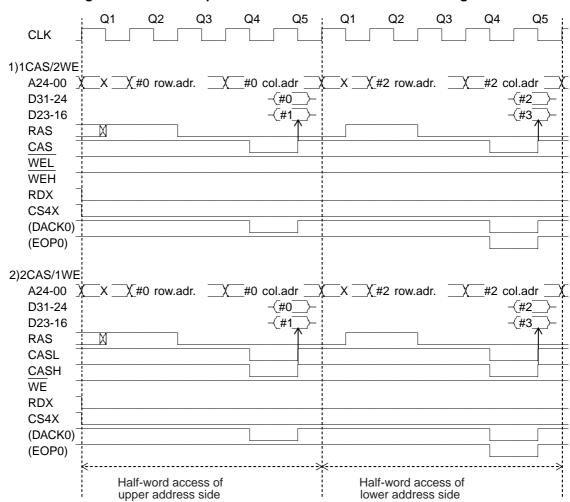

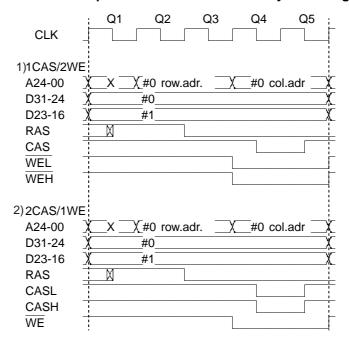

|    | 4.17 | 1.13 DRAM Interface in High-Speed Page Mode              | 182  |

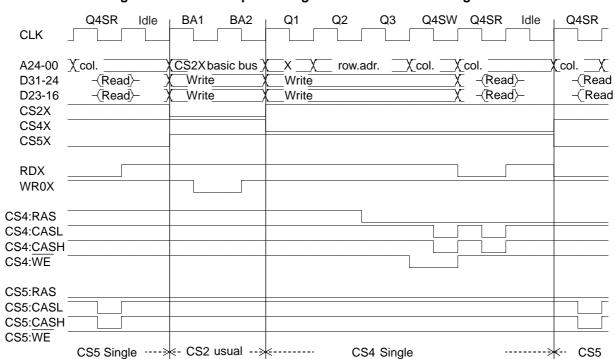

|    | 4.17 | 1.14 Single DRAM Interface: Read                         | 185  |

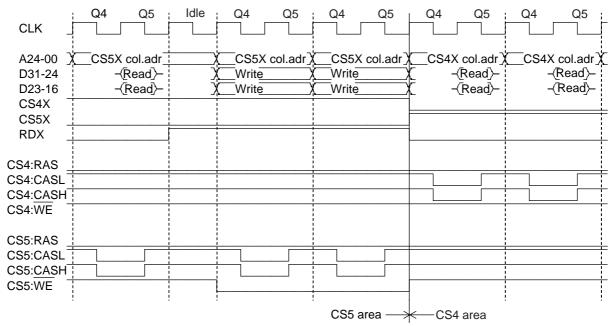

|    | 4.17 | 7.15 Single DRAM Interface: Write                        | 186  |

|    | 4.17 | 16 Single DRAM Interface                                 | 187  |

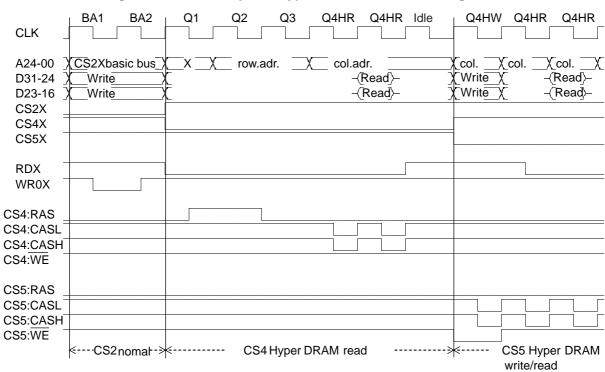

| 4.1               | 7.17 Hyper DRAM Interface: Read                                          | 188 |

|-------------------|--------------------------------------------------------------------------|-----|

| 4.1               | 7.18 Hyper DRAM Interface: Write                                         | 189 |

| 4.1               | 7.19 Hyper DRAM Interface                                                | 190 |

| 4.1               | 7.20 DRAM Refresh                                                        | 191 |

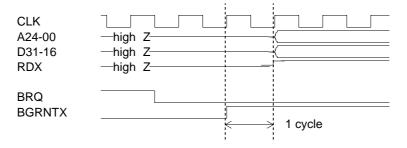

| 4.1               | 7.21 External Bus Request                                                | 193 |

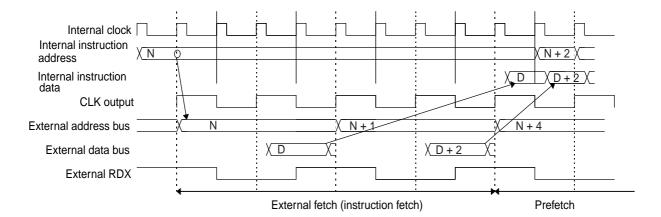

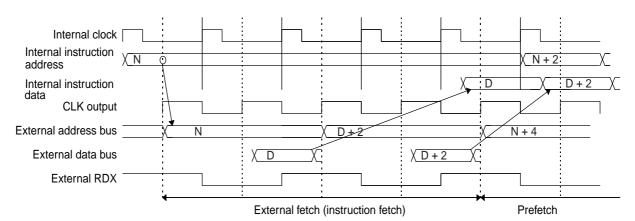

| 4.18              | Internal Clock Multiplication (Clock Doubler)                            | 194 |

| 4.19              | Program Example for External Bus Operation                               | 196 |

| CHAP              | TER 5 I/O PORTS                                                          | 201 |

| 5.1               | Outline of I/O Ports                                                     | 202 |

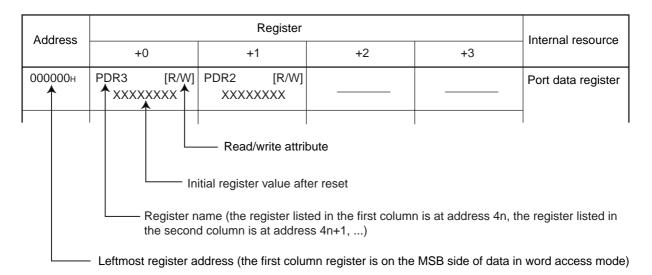

| 5.2               | Port Data Register (PDR)                                                 | 203 |

| 5.3               | Data Direction Register (DDR)                                            | 204 |

| 5.4               | Using External Pins as I/O Ports                                         | 205 |

| CHAP <sup>-</sup> | TER 6 EXTERNAL INTERRUPT/NMI CONTROLLER                                  | 211 |

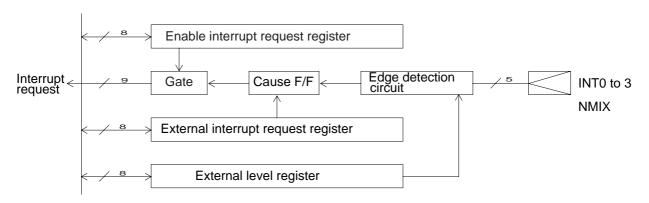

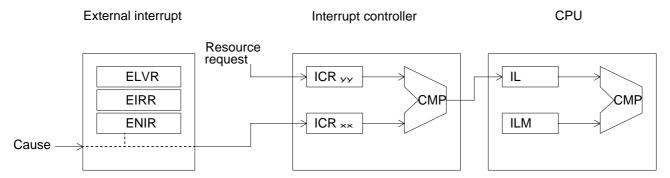

| 6.1               | Overview of External Interrupt/NMI Controller                            | 212 |

| 6.2               | Enable Interrupt Request Register (ENIR)                                 | 213 |

| 6.3               | External Interrupt Request Register (EIRR)                               | 214 |

| 6.4               | External Level Register (ELVR)                                           | 215 |

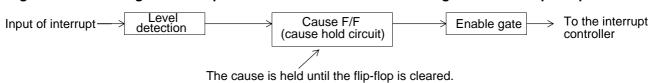

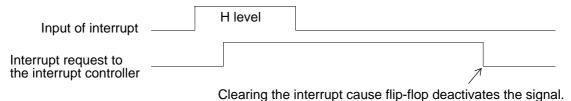

| 6.5               | External Interrupt Operation                                             | 216 |

| 6.6               | External Interrupt Request Levels                                        | 217 |

| 6.7               | Nonmaskable Interrupt (NMI) Operation                                    | 218 |

| CHAP              | TER 7 DELAYED INTERRUPT MODULE                                           | 219 |

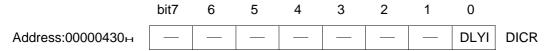

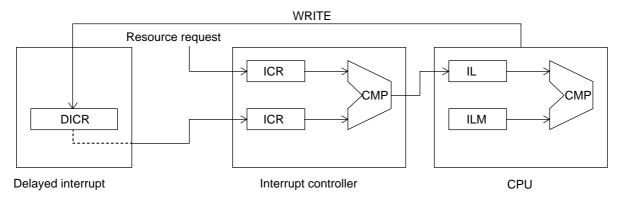

| 7.1               | Overview of Delayed Interrupt Module                                     | 220 |

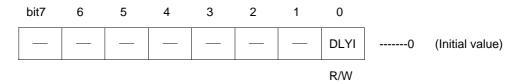

| 7.2               | Delayed Interrupt Control Register (DICR)                                | 221 |

| 7.3               | Operation of Delayed Interrupt Module                                    | 222 |

| CHAP              | TER 8 INTERRUPT CONTROLLER                                               | 223 |

| 8.1               | Overview of Interrupt Controller                                         | 224 |

| 8.2               | Interrupt Controller Block Diagram                                       | 227 |

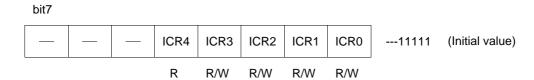

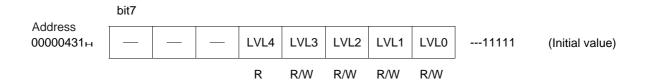

| 8.3               | Interrupt Control Register (ICR)                                         | 228 |

| 8.4               | Hold Request Cancel Request Level Setting Register (HRCL)                | 230 |

| 8.5               | Priority Check                                                           |     |

| 8.6               | Returning from the Standby Mode (Stop/Sleep)                             | 234 |

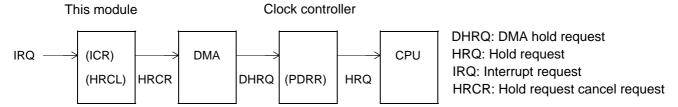

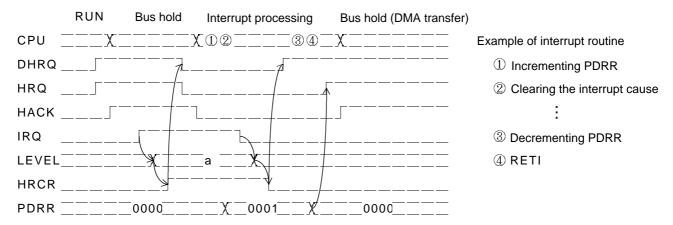

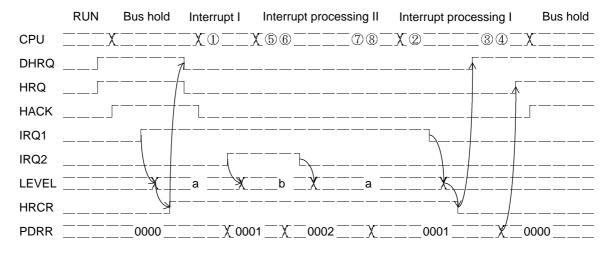

| 8.7               | Hold Request Cancel Request                                              | 235 |

| 8.8               | Example of Using the Hold Request Cancel Request Function (HRCR)         | 236 |

| CHAP              | TER 9 U-TIMER                                                            | 239 |

| 9.1               | Overview of U-TIMER                                                      | 240 |

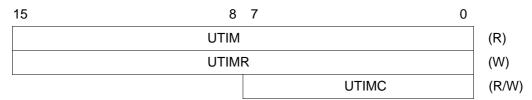

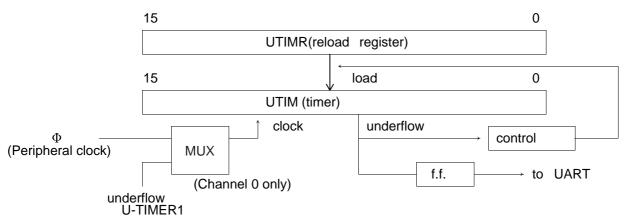

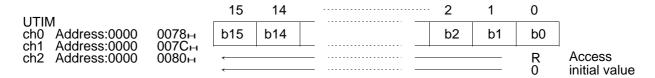

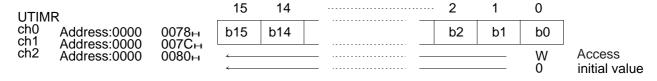

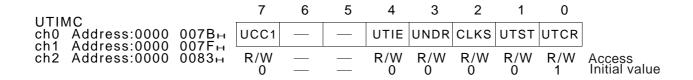

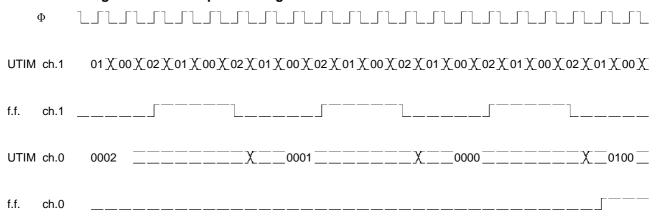

| 9.2               | U-TIMER Registers                                                        | 241 |

| 9.3               | U-TIMER Operation                                                        | 243 |

| CHAP              | TER 10 UART                                                              | 245 |

| 10.1              | Overview of UART                                                         | 246 |

| 10.2              | Serial Mode Register (SMR)                                               | 248 |

| 10.3              | Serial Control Register (SCR)                                            | 250 |

| 10.4              | Serial Input Data Register (SIDR) and Serial Output Data Register (SODR) | 252 |

| 10.5 | 5 Serial Status Register (SSR)                                   | 253 |

|------|------------------------------------------------------------------|-----|

| 10.6 | S UART Operation                                                 | 255 |

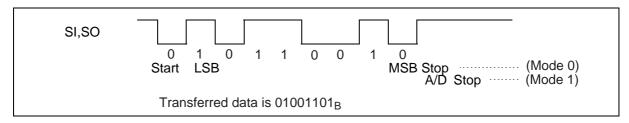

| 10.7 | Asynchronous (Start-Stop) Mode                                   | 257 |

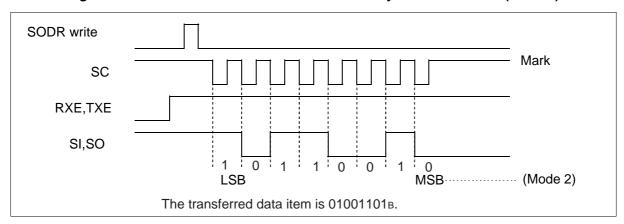

| 10.8 | B CLK Synchronous Mode                                           | 258 |

| 10.9 | UART Interrupt Occurrence and Flag Setting Timing                | 260 |

| 10.1 | 0 Notes on Using the UART and Example for Using the UART         | 263 |

| 10.1 | 1 Setting Examples of Baud Rates and U-TIMER Reload Values       | 265 |

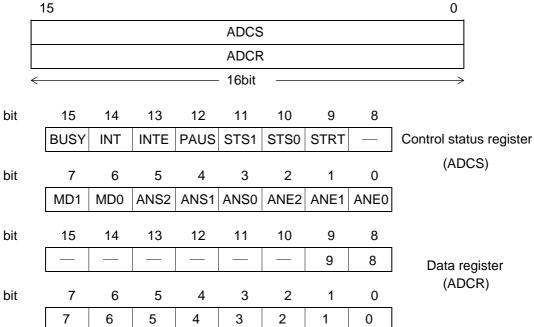

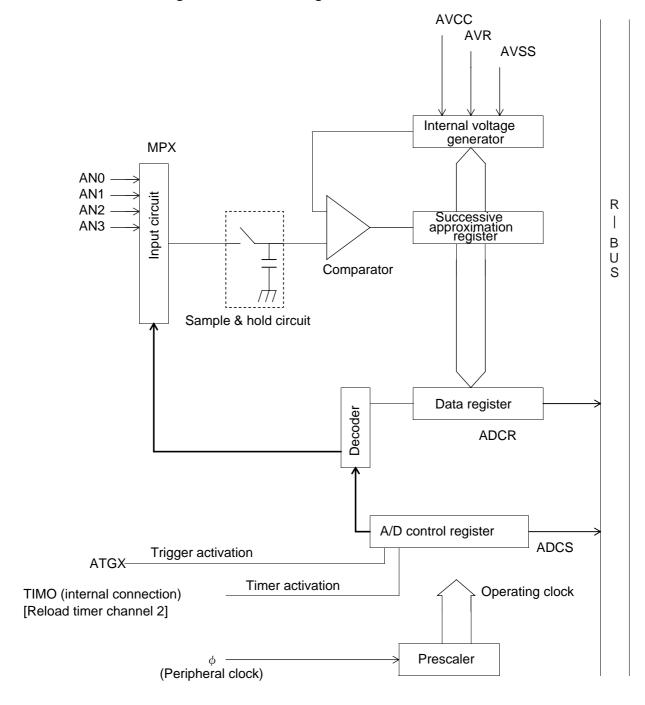

| СНАР | PTER 11 A/D CONVERTER (Successive approximation type)            | 267 |

| 11.1 | Overview of A/D Converter (Successive Approximation Type)        | 268 |

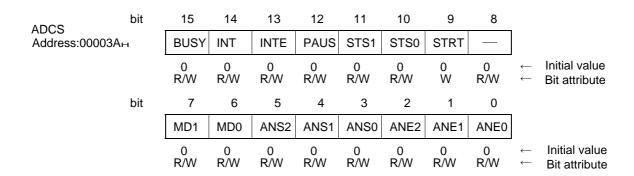

| 11.2 | 2 Control Status Register (ADCS)                                 | 270 |

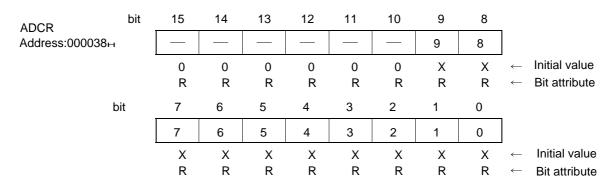

| 11.3 | B Data Register (ADCR)                                           | 275 |

| 11.4 | A/D Converter Operation                                          | 276 |

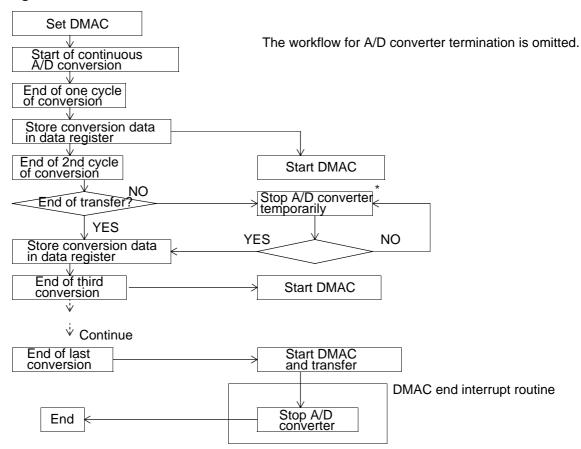

| 11.5 | 5 Conversion Data Protection Function                            | 278 |

| 11.6 | Notes on Using the A/D Converter                                 | 280 |

| СНАР | PTER 12 16-BIT RELOAD TIMER                                      | 281 |

| 12.1 | Overview of 16-bit Reload Timer                                  | 282 |

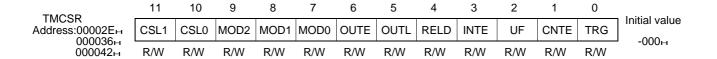

| 12.2 | 2 Control Status Register (TMCSR)                                | 284 |

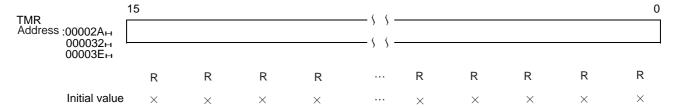

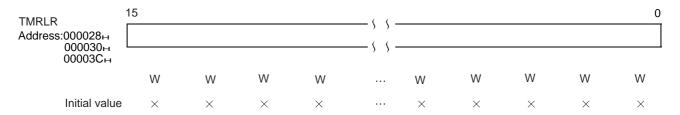

| 12.3 | 3 16-Bit Timer Register (TMR) and 16-Bit Reload Register (TMRLR) | 286 |

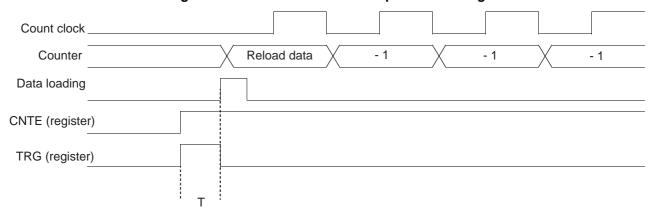

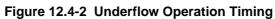

| 12.4 | Operation of 16-Bit Reload Timer                                 | 287 |

| 12.5 | 5 Counter States                                                 | 289 |

| СНАР | PTER 13 BIT SEARCH MODULE                                        | 291 |

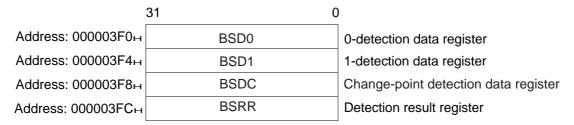

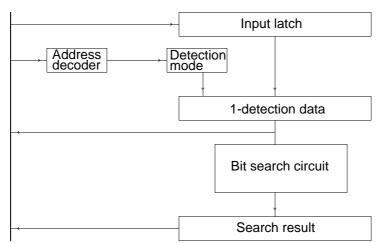

| 13.1 | Overview of the Bit Search Module                                | 292 |

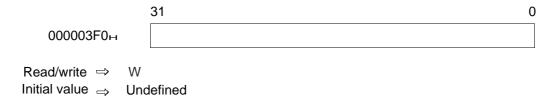

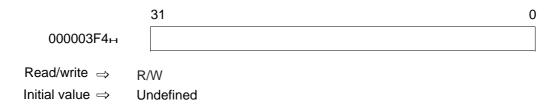

| 13.2 | 2 Bit Search Module Registers                                    | 293 |

| 13.3 | Bit Search Module Operation and Save/Restore Processing          | 295 |

| СНАР | PTER 14 PWM TIMER                                                | 299 |

| 14.1 | Overview of PWM Timer                                            | 300 |

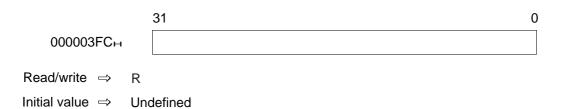

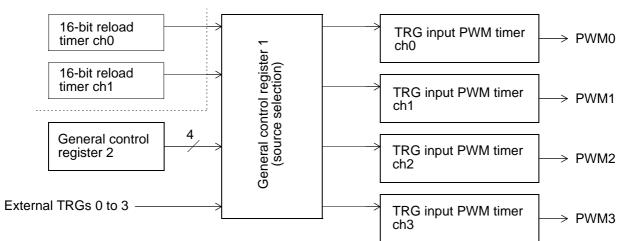

| 14.2 | PWM Timer Block Diagram                                          | 302 |

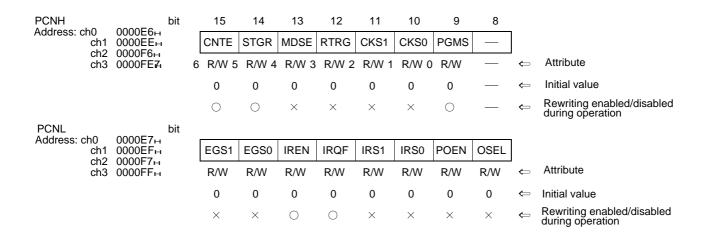

| 14.3 | Control Status Register (PCNH, PCNL)                             | 304 |

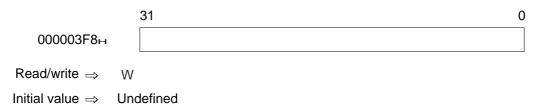

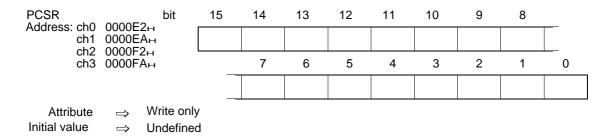

| 14.4 | PWM Cycle Setting Register (PCSR)                                | 308 |

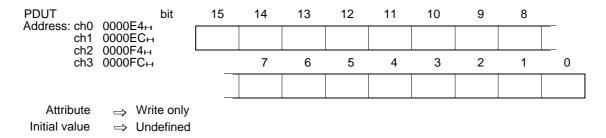

| 14.5 | 5 PWM Duty Cycle Setting Register (PDUT)                         | 309 |

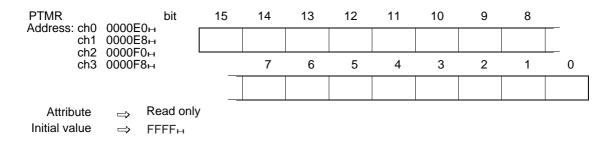

| 14.6 | S PWM Timer Register (PTMR)                                      | 310 |

| 14.7 | General Control Register 1 (GCN1)                                | 311 |

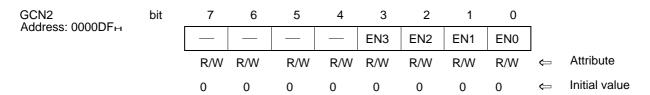

| 14.8 | B General Control Register 2 (GCN2)                              | 314 |

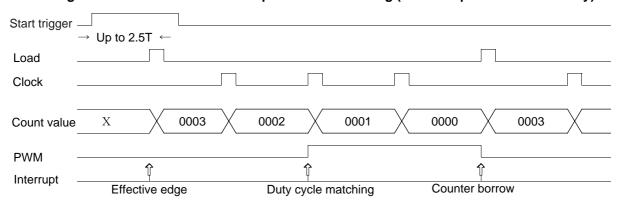

| 14.9 | PWM Operation                                                    | 315 |

| 14.1 | 0 One-Shot Operation                                             | 317 |

| 14.1 | 1 Interrupt                                                      | 319 |

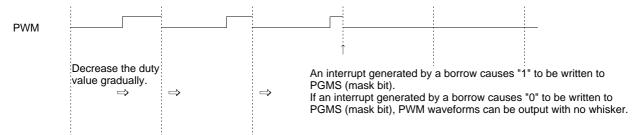

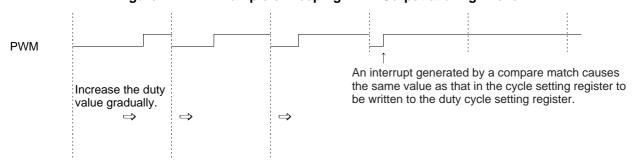

| 14.1 | 2 Constant "L" or Constant "H" Output from PWM Timer             | 320 |

| 14.1 | 3 Starting Multiple PWM Timer Channels                           | 321 |

| СНАР | PTER 15 DMAC                                                     | 323 |

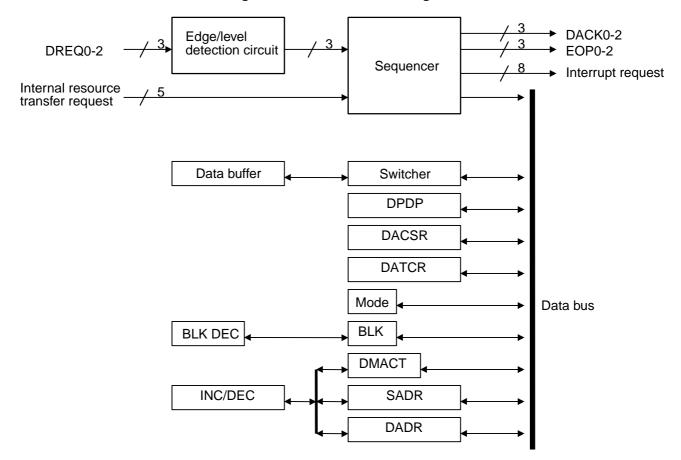

| 15.1 | Overview of DMAC                                                 | 324 |

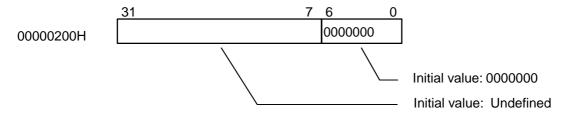

| 15.2 | 2 DMAC Parameter Descriptor Pointer (DPDP)                       | 326 |

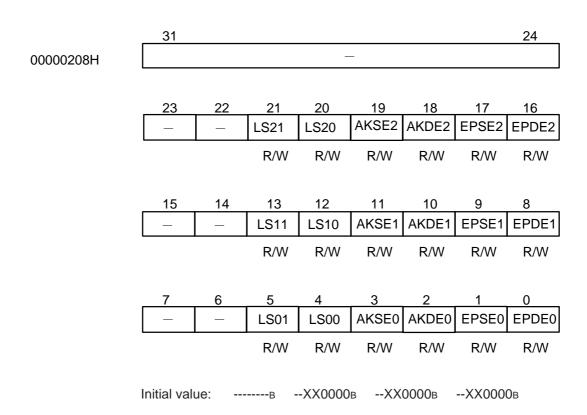

| 15.3 | B DMAC Control Status Register (DACSR)                           | 327 |

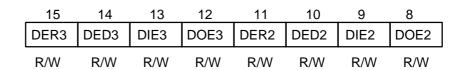

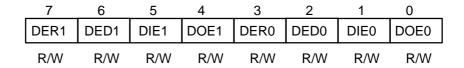

| 15.4 | DMAC Pin Control Register (DATCR)                                | 329 |

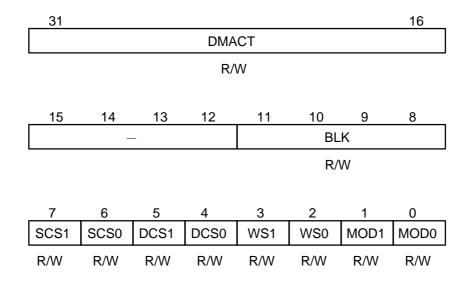

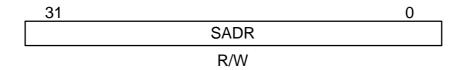

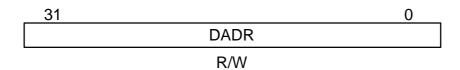

| 15.5 Descriptor Register in RAM                                         | 332 |

|-------------------------------------------------------------------------|-----|

| 15.6 DMAC Transfer Modes                                                | 335 |

| 15.7 Output of Transfer Request Acknowledgment and Transfer End signals | 338 |

| 15.8 Notes on DMAC                                                      | 339 |

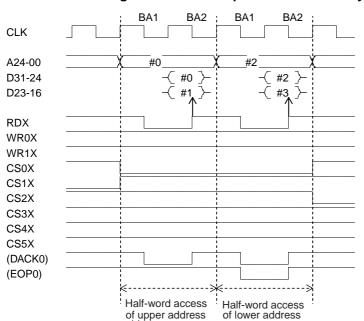

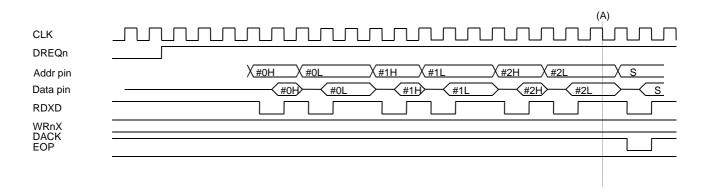

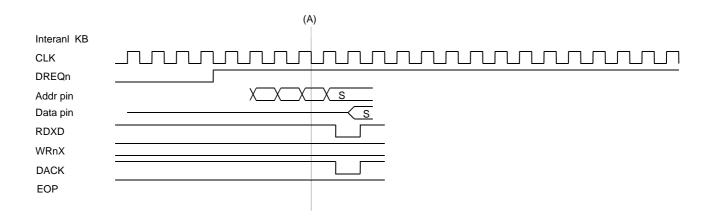

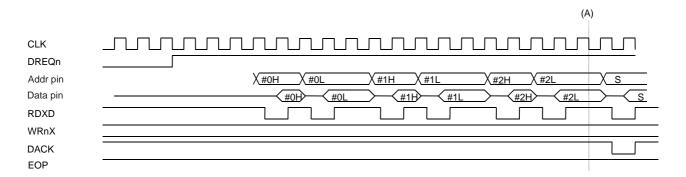

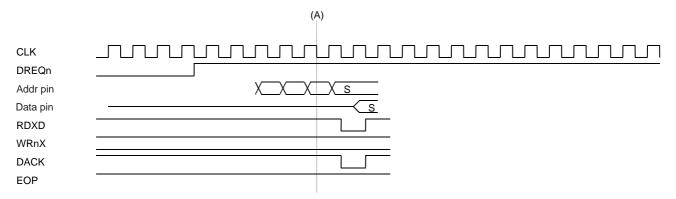

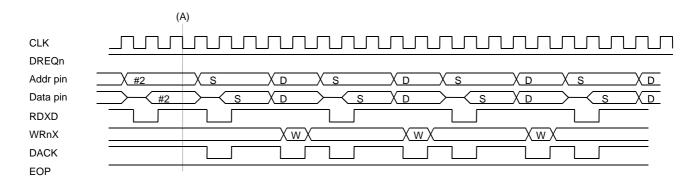

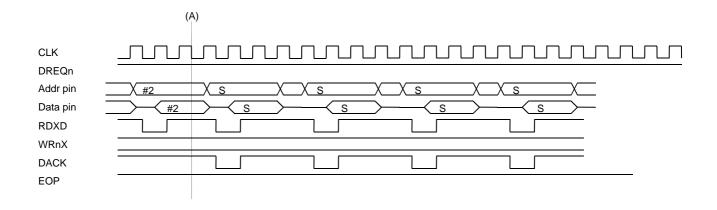

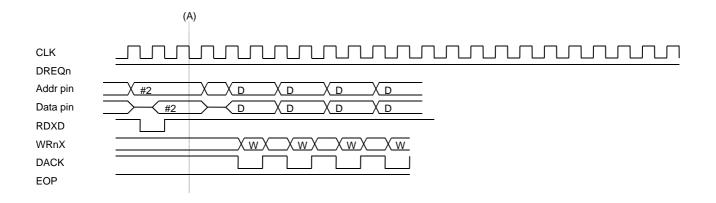

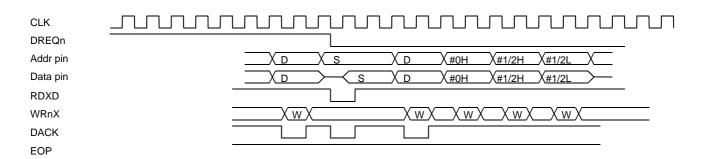

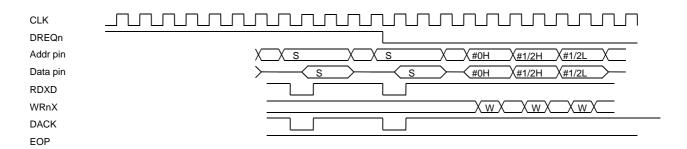

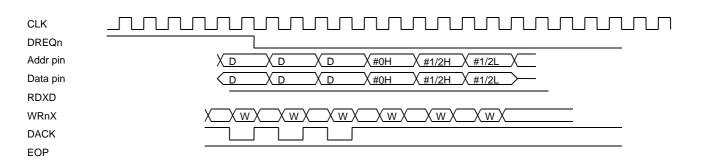

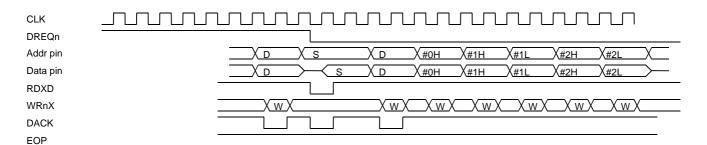

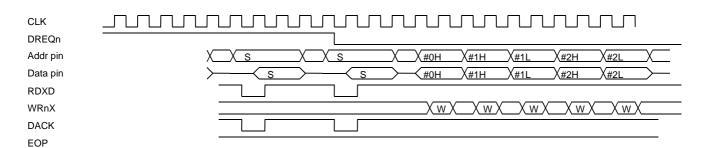

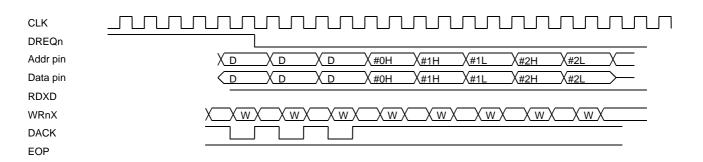

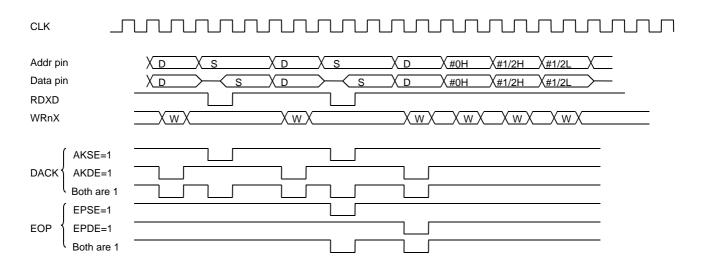

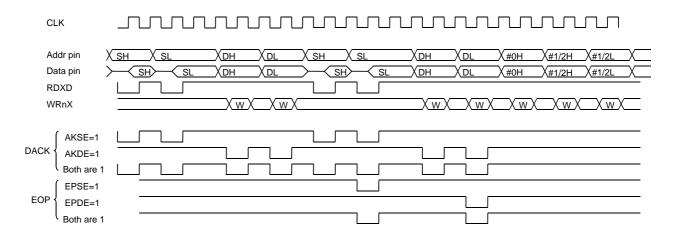

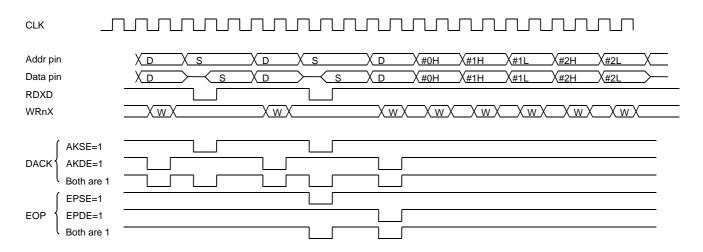

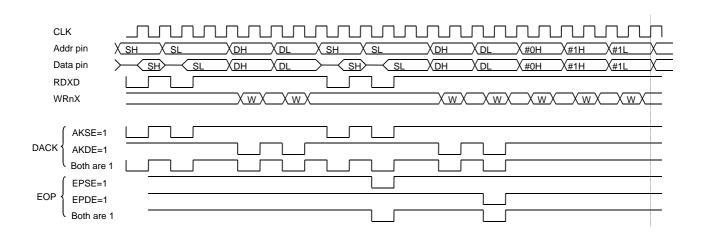

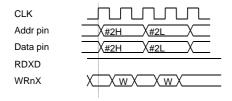

| 15.9 DMAC Timing Charts                                                 | 342 |

| 15.9.1 Timing Charts of the Descriptor Access Block                     | 343 |

| 15.9.2 Timing Charts of Data Transfer Block                             | 345 |

| 15.9.3 Transfer Stop Timing Charts in Continuous Transfer Mode          | 347 |

| 15.9.4 Transfer Termination Timing Charts                               | 349 |

| CHAPTER 16 FLASH MEMORY                                                 | 351 |

| 16.1 Outline of Flash Memory                                            | 352 |

| 16.2 Block Diagram of Flash Memory                                      | 354 |

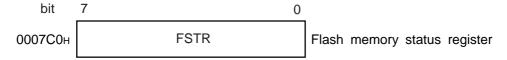

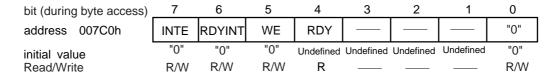

| 16.3 Flash Memory Status Register (FSTR)                                | 355 |

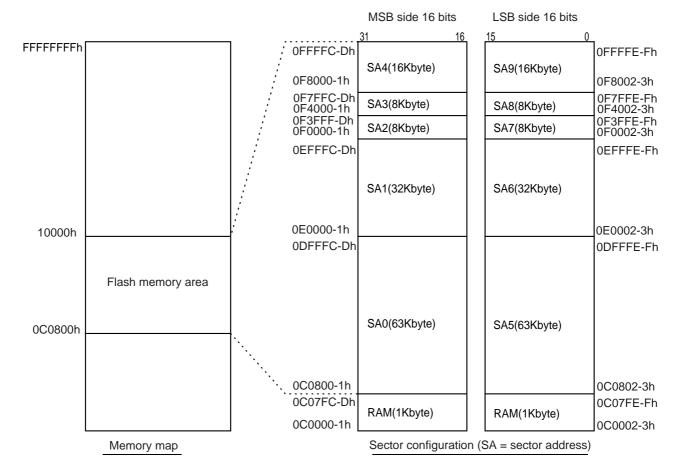

| 16.4 Sector Configuration of Flash Memory                               | 357 |

| 16.5 Flash Memory Access Modes                                          | 359 |

| 16.6 Starting the Automatic Algorithm                                   | 361 |

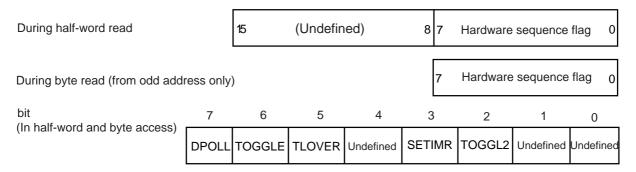

| 16.7 Execution Status of the Automatic Algorithm                        | 364 |

| APPENDIX                                                                | 369 |

| APPENDIX A I/O Maps                                                     | 370 |

| APPENDIX B Interrupt Vectors                                            | 379 |

| APPENDIX C Pin Status for Each CPU Status                               | 383 |

| APPENDIX D Notes on Using Little Endian Areas                           | 395 |

| D.1 C Compiler (fcc911)                                                 | 396 |

| D.2 Assembler (fsm911)                                                  | 399 |

| D.3 Linker (flnk911)                                                    | 401 |

| D.4 Debuggers (sim911, eml911, and mon911)                              | 402 |

| APPENDIX E Instructions                                                 | 403 |

| E.1 FR-Series Instructions                                              | 409 |

| INDEV                                                                   | 42E |

# **FIGURES**

| Figure 1.2-1  | General Block Diagram of MB91F109                                  | 6   |

|---------------|--------------------------------------------------------------------|-----|

| Figure 1.3-1  | Outside Dimensions of FPT-100P-M06                                 | 7   |

| Figure 1.3-2  | Outside Dimensions of FPT-100P-M05                                 | 8   |

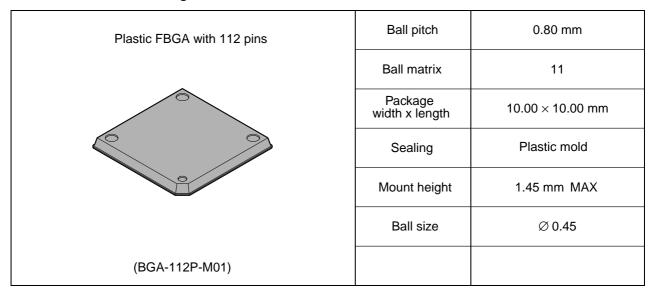

| Figure 1.3-3  | Outside Dimensions of BGA-112P-M01                                 | 9   |

| Figure 1.4-1  | QFP-100 Pin Arrangements                                           | 10  |

| Figure 1.4-2  | LQFP-100 Pin Arrangements                                          | 11  |

| Figure 1.4-3  | FBGA-112 Pin Arrangements                                          | 12  |

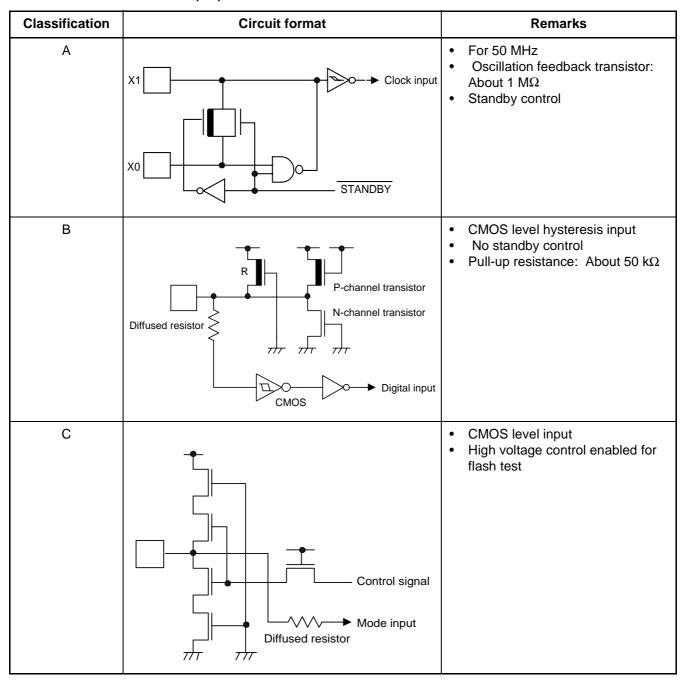

| Figure 1.7-1  | MB91F109 Memory Map                                                | 24  |

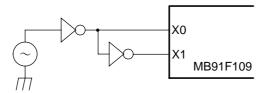

| Figure 1.8-1  | Example of Using an External Clock (Normal Method)                 | 26  |

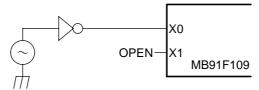

| Figure 1.8-2  | Example of Using an External Clock (Possible at 12.5 MHz or Lower) | 27  |

| Figure 2.2-1  | Internal Architecture                                              | 31  |

| Figure 2.2-2  | Instruction Pipeline                                               | 32  |

| Figure 2.3-1  | Configuration of general-purpose registers                         | 33  |

| Figure 2.3-2  | Configuration of special registers                                 | 34  |

| Figure 2.3-3  | Configuration of General-Purpose Registers                         | 35  |

| Figure 2.3-4  | Configuration of Special Registers                                 | 36  |

| Figure 2.4-1  | Data Mapping in Bit Ordering Mode                                  | 42  |

| Figure 2.4-2  | Data Mapping in Byte Ordering Mode                                 | 42  |

| Figure 2.6-1  | MB91F109 Memory Map                                                | 44  |

| Figure 2.6-2  | Memory Map Common to the FR Series.                                | 45  |

| Figure 2.8-1  | Example of Interrupt Stack                                         | 58  |

| Figure 2.8-2  | Example of Multiple EIT Processing                                 | 63  |

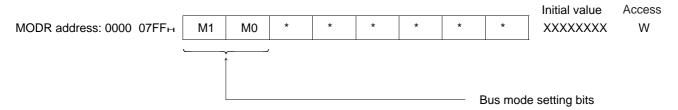

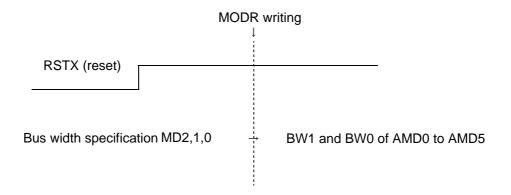

| Figure 2.10-1 | Mode Register Configuration                                        | 70  |

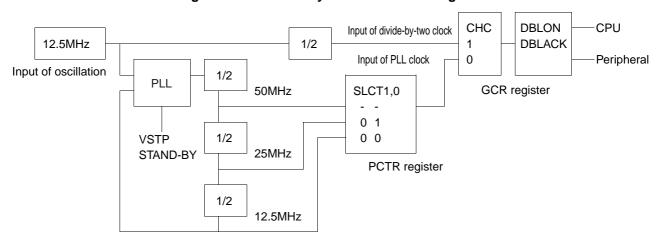

| Figure 3.1-1  | Clock Generator and Controller Registers                           | 74  |

| Figure 3.1-2  | Block Diagram of the Clock Generator and Controller                | 75  |

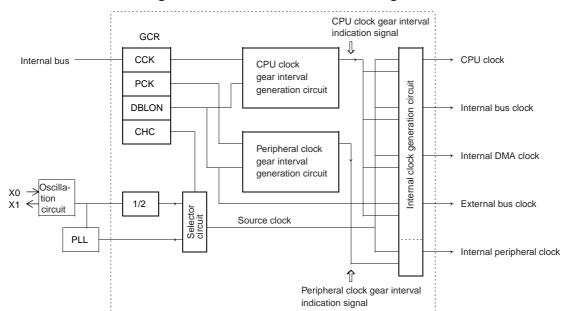

| Figure 3.9-1  | Gear Controller Block Diagram                                      | 87  |

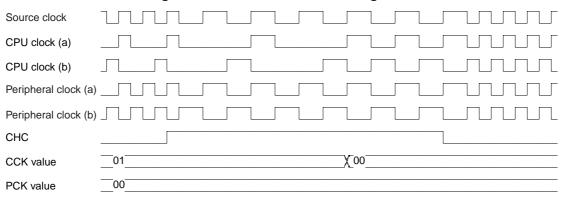

| Figure 3.9-2  | Clock Selection Timing Chart                                       | 89  |

| Figure 3.10-1 | Stop Controller Block Diagram                                      | 92  |

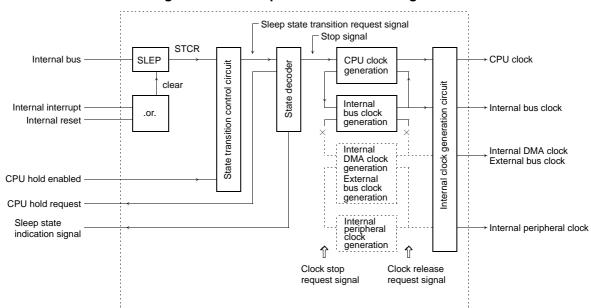

| Figure 3.10-2 | Sleep Controller Block Diagram                                     | 95  |

| Figure 3.10-3 | Standby Mode State Transition                                      | 98  |

| Figure 3.11-1 | Watchdog Timer Block Diagram                                       | 99  |

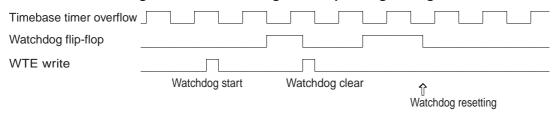

| Figure 3.11-2 | Watchdog Timer Operating Timing                                    | 100 |

| Figure 3.11-3 | Timebase Timer Counter                                             | 100 |

| Figure 3.12-1 | Block Diagram of Reset Source Hold Circuit                         | 101 |

| Figure 3 13-1 | DMA Suppression Circuit Block Diagram                              | 103 |

| Figure 3.15-1  | Example of PLL Clock Setting                                                           | 108 |

|----------------|----------------------------------------------------------------------------------------|-----|

| Figure 3.15-2  | Clock System Reference Diagram                                                         | 109 |

| Figure 4.1-1   | Bus Interface Registers                                                                | 113 |

| Figure 4.1-2   | Bus Interface Block Diagram                                                            | 114 |

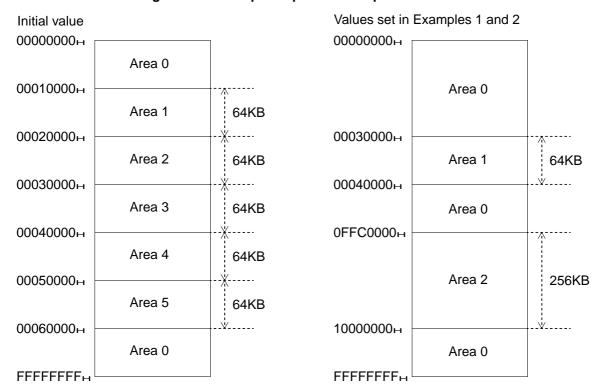

| Figure 4.2-1   | Example of Setting Chip Select Areas                                                   | 115 |

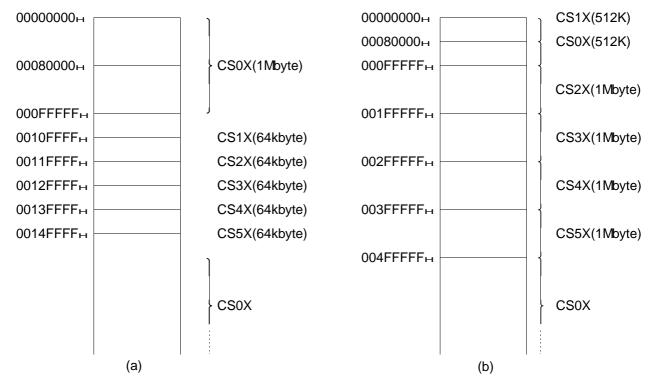

| Figure 4.4-1   | Sample Maps of the Chip Select Areas                                                   | 120 |

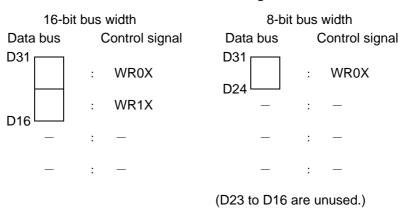

| Figure 4.16-1  | Data bus Widths and Control Signals in Usual Bus Interface                             | 139 |

| Figure 4.16-2  | Data Bus Widths and Control Signals in DRAM Interface                                  | 139 |

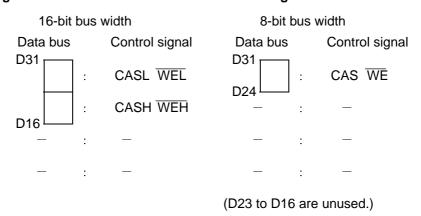

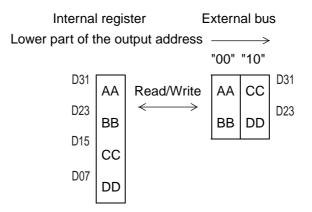

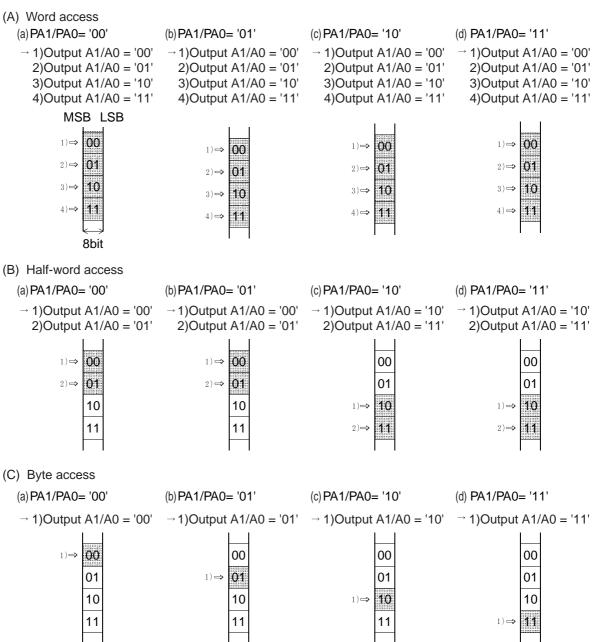

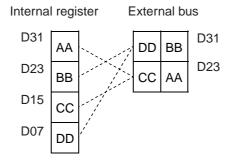

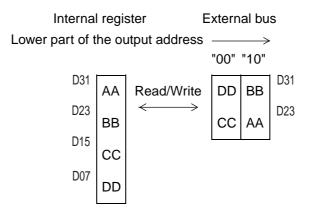

| Figure 4.16-3  | Relationship between Internal Register and External Data Bus for Word Access           | 141 |

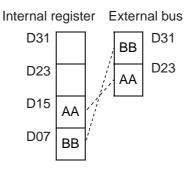

| Figure 4.16-4  | Relationship between Internal Register and External Data Bus for Half-Word Access      | 141 |

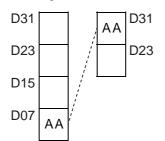

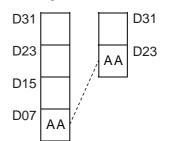

| Figure 4.16-5  | Relationship between Internal Register and External Data Bus for Byte Access           | 142 |

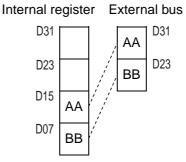

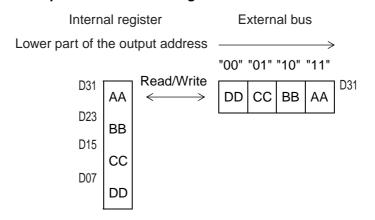

| Figure 4.16-6  | Relationship between Internal Register and External Data Bus for 16-bit Bus Width      | 142 |

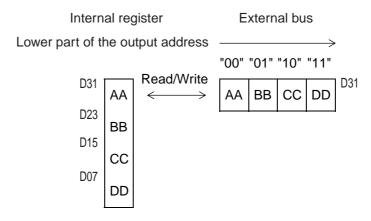

| Figure 4.16-7  | Relationship between Internal Register and External Data Bus for 8-bit Bus Width       | 143 |

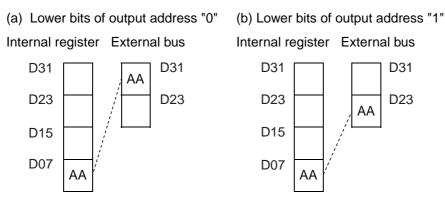

| Figure 4.16-8  | External Bus Access for 16-bit Bus Width                                               | 144 |

| Figure 4.16-9  | External Bus Access for 8-bit Bus Width                                                | 145 |

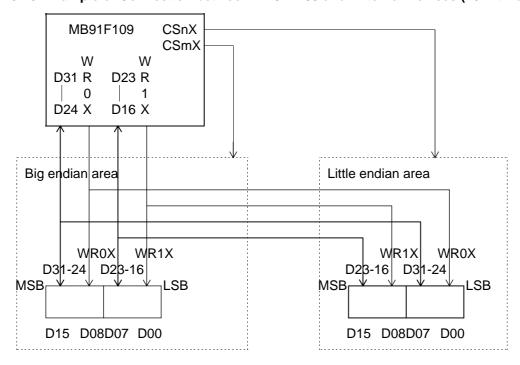

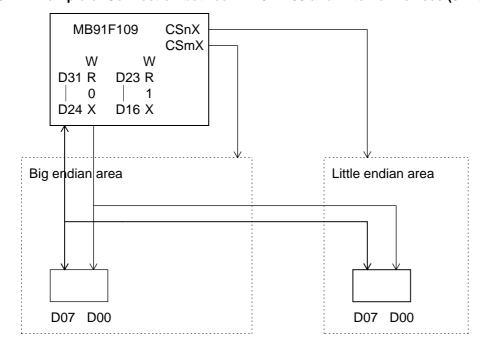

| Figure 4.16-10 | Example of Connection between MB91F109 and External Devices                            | 146 |

| Figure 4.16-11 | Relationship between Internal Register and External Data Bus for Word Access           | 147 |

| Figure 4.16-12 | Relationship between Internal Register and External Data Bus for Half-word Access      | 148 |

| Figure 4.16-13 | Relationship between Internal Register and External Data Bus for Byte Access           | 148 |

| Figure 4.16-14 | Relationship between Internal Register and External Data Bus for 16-bit Bus Width      | 149 |

| Figure 4.16-15 | Relationship between Internal Register and External Data Bus for 8-bit Bus Width       | 149 |

| Figure 4.16-16 | Example of Connection between MB91F109 and External Devices (16-Bit Bus Width)         | 150 |

| Figure 4.16-17 | Example of Connection between MB91F109 and External Devices (8-Bit Bus Width)          | 150 |

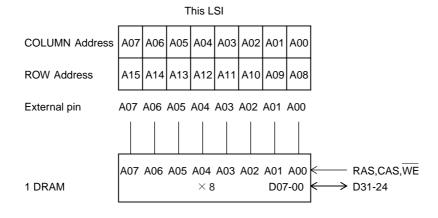

| Figure 4.16-18 | Example of Connection between MB91F109 and One 8-bit Output DRAM (8-Bit Data Bus) $$ . | 156 |

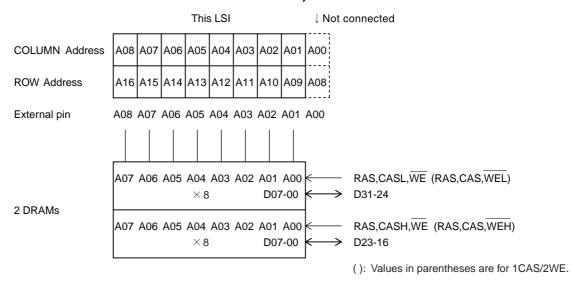

| Figure 4.16-19 | Example of Connection between MB91F109 and Two 8-Bit Output DRAMs (16-Bit Data Bus)    | 157 |

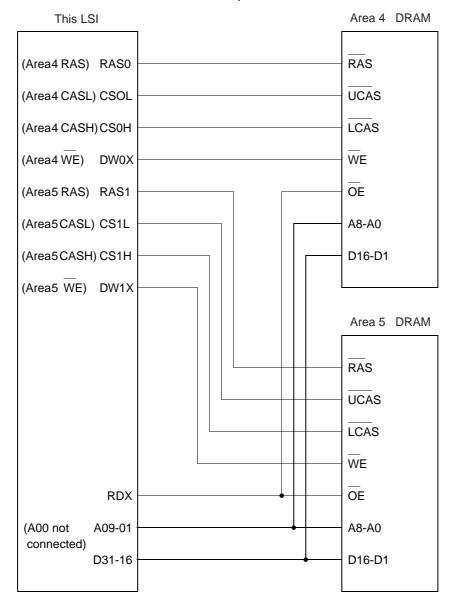

| Figure 4.16-20 | Example of Connection between MB91F109 and Two 16-Bit Output DRAMs (16-Bit Data Bus)   | 158 |

| Figure 4.17-1  | Example of Basic Read Cycle Timing Chart                                               | 162 |

| Figure 4.17-2  | Example for Basic Write Cycle Timing                                                   | 164 |

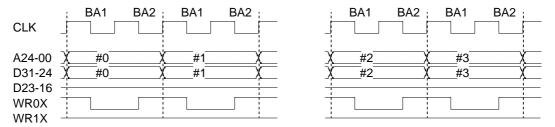

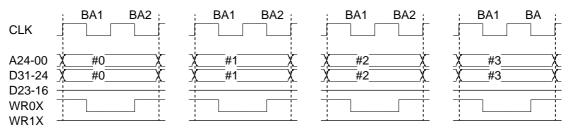

| Figure 4.17-3  | Example 1 of Read Cycle Timing Chart                                                   | 166 |

| Figure 4.17-4  | Example 2 of Read Cycle Timing Chart                                                   | 166 |

| Figure 4.17-5  | Example 3 of Read Cycle Timing Chart                                                   | 166 |

| Figure 4.17-6  | Example 4 of Read Cycle Timing Chart                                                   | 167 |

| Figure 4.17-7  | Example 5 of Read Cycle Timing Chart                                                   | 167 |

| Figure 4.17-8  | Example 1 of Write Cycle Timing Chart                                                  | 168 |

| Figure 4.17-9  | Example 2 of Write Cycle Timing Chart                                                  | 168 |

| Figure 4.17-10 | Example 3 of Write Cycle Timing Chart                                                  | 168 |

| Figure 4.17-11 | Example 4 of Write Cycle Timing Chart                                                  | 169 |

| Figure 4.17-12 | Example 5 of Write Cycle Timing Chart                                                                 | 169 |

|----------------|-------------------------------------------------------------------------------------------------------|-----|

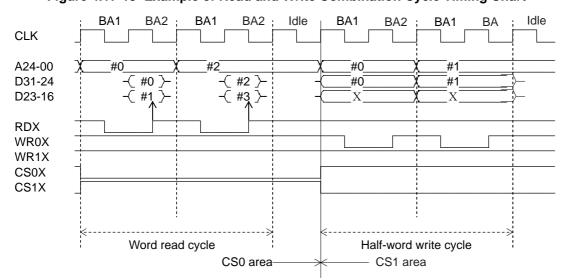

| Figure 4.17-13 | Example of Read and Write Combination Cycle Timing Chart                                              | 170 |

| Figure 4.17-14 | Example of Automatic Wait Cycle Timing Chart                                                          | 171 |

| Figure 4.17-15 | Example of External Wait Cycle Timing Chart                                                           | 172 |

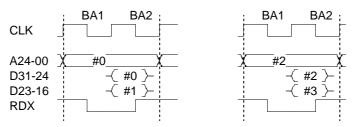

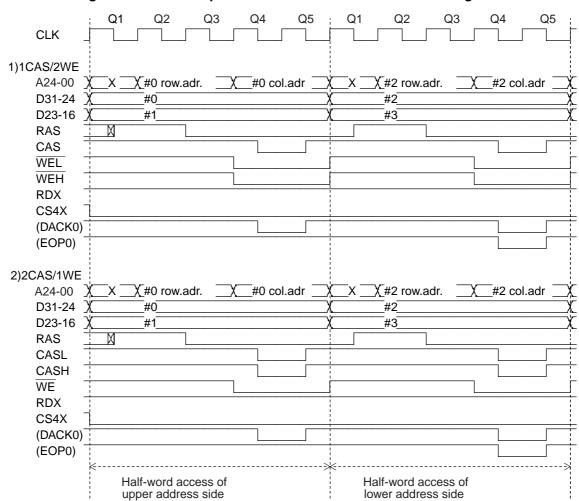

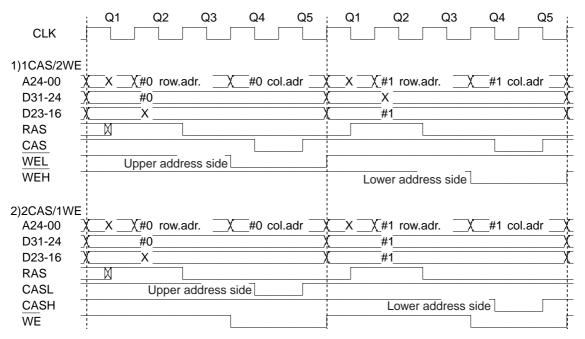

| Figure 4.17-16 | Example of Usual DRAM Interface Read Timing Chart                                                     | 173 |

| Figure 4.17-17 | Example of Usual DRAM Interface Write Timing Chart                                                    | 175 |

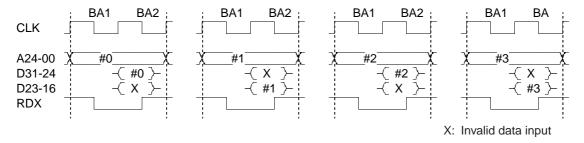

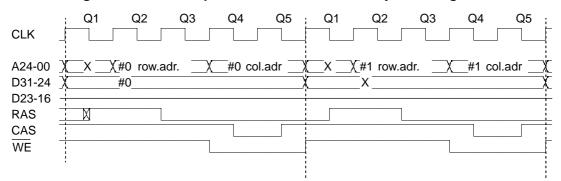

| Figure 4.17-18 | Example 1 of Usual DRAM Read Cycle Timing Chart                                                       | 177 |

| Figure 4.17-19 | Example 2 of Usual DRAM Read Cycle Timing Chart                                                       | 178 |

| Figure 4.17-20 | Example 3 of Usual DRAM Read Cycle Timing Chart                                                       | 178 |

| Figure 4.17-21 | Example 1 of Usual DRAM Write Cycle Timing Chart                                                      | 179 |

| Figure 4.17-22 | Example 2 of Usual DRAM Write Cycle Timing Chart                                                      | 180 |

| Figure 4.17-23 | Example 3 of Usual DRAM Write Cycle Timing Chart                                                      | 180 |

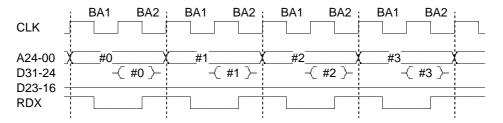

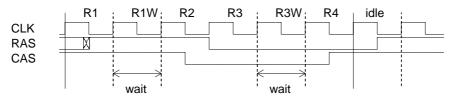

| Figure 4.17-24 | Example of Automatic Wait Cycle Timing Chart in Usual DRAM Interface                                  | 181 |

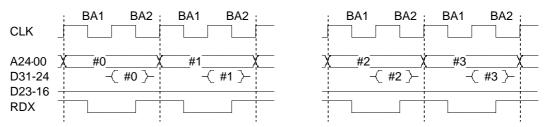

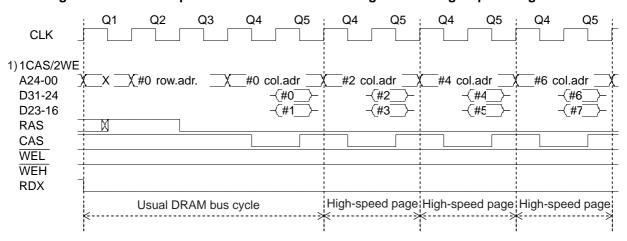

| Figure 4.17-25 | Example 1 of DRAM Interface Timing Chart in High-Speed Page Mode                                      | 182 |

| Figure 4.17-26 | Example 2 of DRAM Interface Timing Chart in High-Speed Page Mode                                      | 182 |

| Figure 4.17-27 | Example 3 of DRAM Interface Timing Chart in High-Speed Page Mode                                      | 183 |

| Figure 4.17-28 | Example 4 of DRAM Interface Timing Chart in High-Speed Page Mode                                      | 184 |

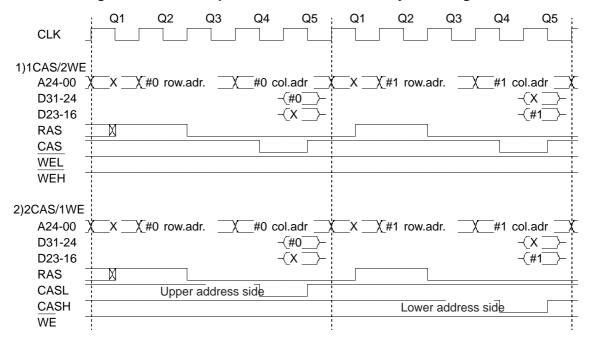

| Figure 4.17-29 | Example of Single DRAM Interface Read Timing Chart                                                    | 185 |

| Figure 4.17-30 | Example of Single DRAM Interface Write Timing Chart                                                   | 186 |

| Figure 4.17-31 | Example of Single DRAM Interface Timing Chart                                                         | 187 |

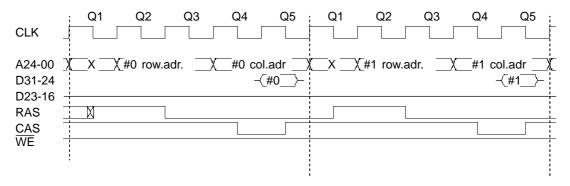

| Figure 4.17-32 | Example of Hyper DRAM Interface Read Timing Chart                                                     | 188 |

| Figure 4.17-33 | Example of Hyper DRAM Interface Write Timing Chart                                                    | 189 |

| Figure 4.17-34 | Example of Hyper DRAM Interface Timing Chart                                                          | 190 |

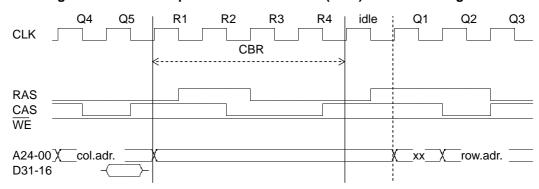

| Figure 4.17-35 | Example of CAS before RAS (CBR) Refresh Timing Chart                                                  | 191 |

| Figure 4.17-36 | Example of Timing Chart of CBR Refresh Automatic Wait Cycle                                           | 192 |

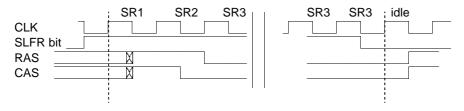

| Figure 4.17-37 | Example of Selfrefresh Timing Chart                                                                   | 192 |

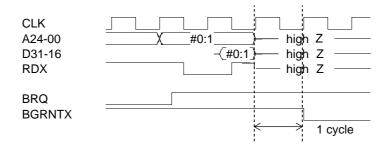

| Figure 4.17-38 | Example of Bus Control Release Timing Chart                                                           | 193 |

| Figure 4.17-39 | Example of Bus Control Acquisition Timing                                                             | 193 |

| Figure 4.18-1  | Example of Timing Chart for 2X Clock (BW-16bit, Access-Word Read)                                     | 194 |

| Figure 4.18-2  | Example of Timing for 1X Clock (BW-16bit, Access-Word Read)                                           | 195 |

| Figure 5.1-1   | Basic I/O Port Block Diagram                                                                          | 202 |

| Figure 6.1-1   | External Interrupt/NMI Controller Registers                                                           | 212 |

| Figure 6.1-2   | External Interrupt/NMI Controller Block Diagram                                                       | 212 |

| Figure 6.5-1   | External Interrupt Operation                                                                          | 216 |

| Figure 6.6-1   | Clearing the Interrupt Cause Hold Circuit at Level Setting for the Interrupt Request Mode             | 217 |

| Figure 6.6-2   | Input of an Interrupt Cause in Interrupt Enable Mode and a Request Issued to the Interrupt Controller | 217 |

| Figure 6.7-1   | NMI Request Detection Block                                                                           | 218 |

| Figure 7.1-1   | Delayed Interrupt Module Register                                                          | 220 |

|----------------|--------------------------------------------------------------------------------------------|-----|

| Figure 7.1-2   | Delayed Interrupt Module Block Diagram                                                     | 220 |

| Figure 8.1-1   | Interrupt Controller Registers (1/2)                                                       | 225 |

| Figure 8.1-2   | Interrupt Controller Registers (2/2)                                                       | 226 |

| Figure 8.2-1   | Block Diagram of the Interrupt Controller                                                  | 227 |

| Figure 8.8-1   | Example of Hardware Configuration for Using the Hold Request Cancel Request Function       | 236 |

| Figure 8.8-2   | Example of Timing for Hold Request Cancel Request Sequence (Interrupt Level: HRCL > a)     | 237 |

| Figure 8.8-3   | Example of Timing for Hold Request Cancel Request Sequence (Interrupt Level: HRCL > a > b) | 237 |

| Figure 9.1-1   | U-TIMER Registers                                                                          | 240 |

| Figure 9.1-2   | U-TIMER Block Diagram                                                                      | 240 |

| Figure 9.3-1   | Example of Using U-TIMER Channels 0 and 1 in Cascade Mode                                  | 243 |

| Figure 10.1-1  | UART Registers                                                                             | 246 |

| Figure 10.1-2  | UART Block Diagram                                                                         | 247 |

| Figure 10.7-1  | Format of Data Transferred in Asynchronous (Start-Stop) Mode (Mode 0 or 1)                 | 257 |

| Figure 10.8-1  | Format of Data Transferred in CLK Synchronous Mode (Mode 2)                                | 258 |

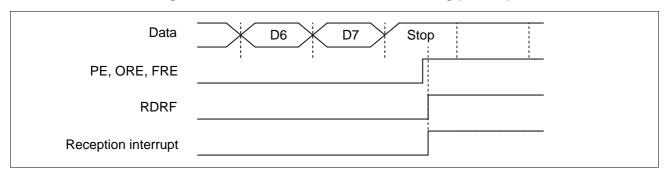

| Figure 10.9-1  | ORE, FRE, and RDRF Set Timing (Mode 0)                                                     | 260 |

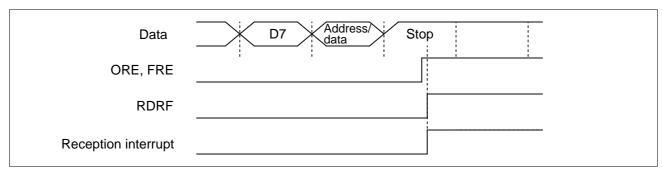

| Figure 10.9-2  | ORE, FRE, and RDRF Set Timing (Mode 1)                                                     | 261 |

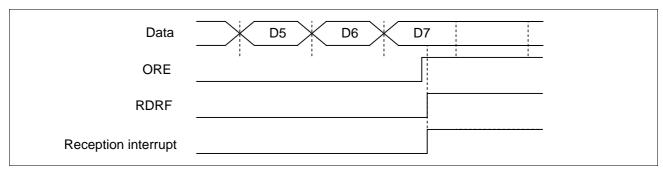

| Figure 10.9-3  | ORE and RDRF Set Timing (Mode 2)                                                           | 261 |

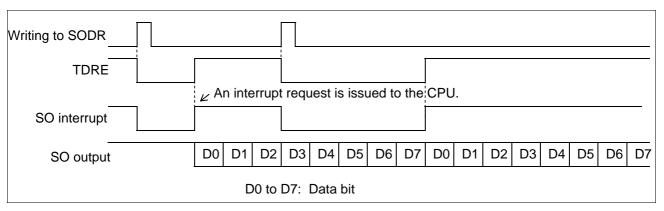

| Figure 10.9-4  | TDRE Set Timing (Mode 0 or 1)                                                              | 262 |

| Figure 10.9-5  | TDRE Set Timing (Mode 2)                                                                   | 262 |

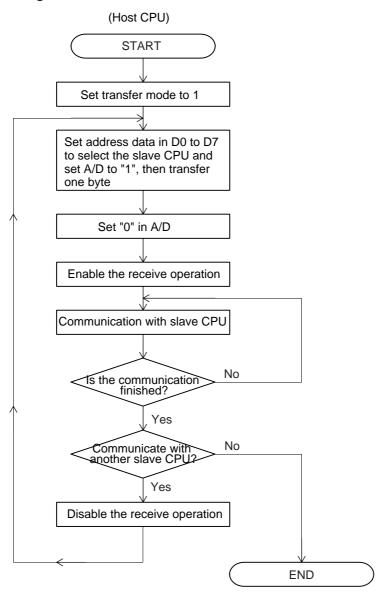

| Figure 10.10-1 | Sample System Structure for Mode 1                                                         | 263 |

| Figure 10.10-2 | Communication Flowchart for Mode 1                                                         | 264 |

| Figure 11.1-1  | A/D Converter Registers                                                                    | 268 |

| Figure 11.1-2  | Block Diagram of the A/D Converter.                                                        | 269 |

| Figure 11.5-1  | Workflow of the Data Protection Function when DMA Transfer is Used                         | 279 |

| Figure 12.1-1  | 16-Bit Reload Timer Registers                                                              | 282 |

| Figure 12.1-2  | 16-Bit Reload Timer Block Diagram                                                          | 283 |

| Figure 12.4-1  | Counter Start and Operation Timing                                                         | 287 |

| Figure 12.4-2  | Underflow Operation Timing                                                                 | 288 |

| Figure 12.5-1  | Counter States Transition                                                                  | 289 |

| Figure 13.1-1  | Bit Search Module Registers                                                                | 292 |

| Figure 13.1-2  | Block Diagram of the Bit Search Module                                                     | 292 |

| Figure 14.1-1  | PWM Timer Registers                                                                        | 301 |

| Figure 14.2-1  | General Block Diagram of PWM Timer                                                         | 302 |

| Figure 14.2-2  | Block Diagram of Single PWM Timer Channel                                                  | 303 |

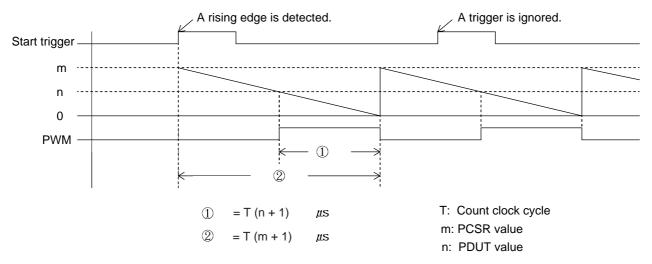

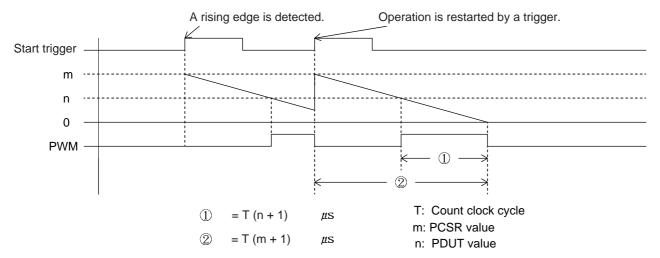

| Figure 14.9-1  | PWM Operation Timing Chart (Trigger Restart Disabled)                                      | 316 |

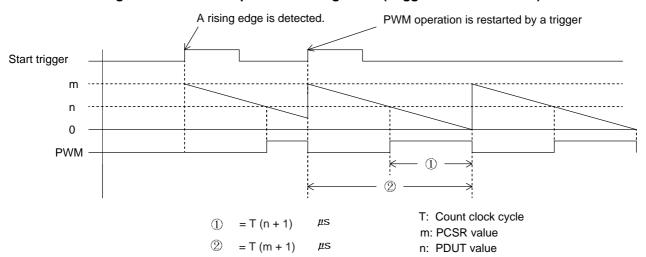

| Figure 14.9-2  | PWM Operation Timing Chart (Trigger Restart Enabled)                                       | 316 |

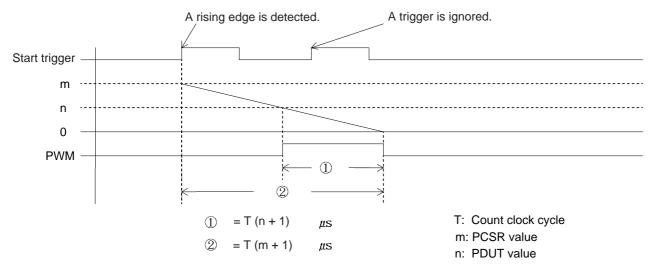

| Figure 14.10-1 | One-Shot Operation Timing Chart (Trigger Restart Disabled)          | 318 |

|----------------|---------------------------------------------------------------------|-----|

| Figure 14.10-2 | One-Shot Operation Timing Chart (Trigger Restart Enabled)           | 318 |

| Figure 14.11-1 | Causes of Interrupts and Their Timing (PWM Output: Normal Polarity) | 319 |

| Figure 14.12-1 | Example of Keeping PWM Output at a Lower Level                      | 320 |

| Figure 14.12-2 | Example of Keeping PWM Output at a High Level                       | 320 |

| Figure 15.1-1  | DMAC Registers                                                      | 324 |

| Figure 15.1-2  | DMAC Block Diagram                                                  | 325 |

| Figure 16.1-1  | Flash Memory Registers                                              | 352 |

| Figure 16.2-1  | Block diagram of the Flash Memory                                   | 354 |

| Figure 16.4-1  | Memory Map and Sector Configuration                                 | 357 |

| Figure 16.7-1  | Structure of the Hardware Sequence Flag                             | 364 |

# **TABLES**

| Table 1.4-1  | FBGA Package Pin Names                                                                                  | 13  |

|--------------|---------------------------------------------------------------------------------------------------------|-----|

| Table 1.5-1  | Pin Functions (1/5)                                                                                     | 14  |

| Table 1.5-2  | Pin Functions (2/5)                                                                                     | 15  |

| Table 1.5-3  | Pin Functions (3/5)                                                                                     | 17  |

| Table 1.5-4  | Pin Functions (4/5)                                                                                     | 18  |

| Table 1.5-5  | Pin Functions (5/5)                                                                                     | 20  |

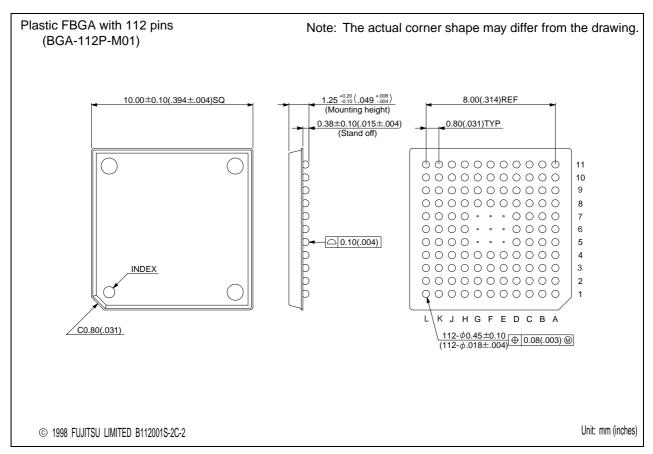

| Table 1.6-1  | I/O circuit format (1/2)                                                                                | 22  |

| Table 1.6-2  | I/O circuit format (1/2)                                                                                | 23  |

| Table 2.8-1  | Interrupt Level                                                                                         | 54  |

| Table 2.8-2  | Assignments of Interrupt Causes and Interrupt Vectors                                                   | 56  |

| Table 2.8-3  | Vector Table                                                                                            | 61  |

| Table 2.8-4  | Priority for EIT Event Acceptance and Masking Other Events                                              | 62  |

| Table 2.8-5  | EIT Handler Execution Order                                                                             | 63  |

| Table 2.10-1 | Mode Pins and Setting Modes                                                                             | 69  |

| Table 2.10-2 | Bus Mode Setting Bit and the Function                                                                   | 70  |

| Table 3.2-1  | Watchdog Timer Cycles Specified by WT1 and WT0                                                          | 77  |

| Table 3.3-1  | Oscillation Stabilization Wait Time Specified by OSC1 and OSC0                                          | 79  |

| Table 3.6-1  | CPU Machine Clock                                                                                       | 82  |

| Table 3.6-2  | Peripheral Machine Clock                                                                                | 83  |

| Table 3.7-1  | Watchdog Timer Cycles Specified by WT1 and WT0                                                          | 85  |

| Table 3.10-1 | Types of Operation in Standby Mode                                                                      | 90  |

| Table 3.14-1 | Operating Frequency Combinations Depending on whether the Clock Doubler Function is Enabled or Disabled | 107 |

| Table 4.3-1  | Correspondence between Chip Select Areas and Selectable Bus Interfaces                                  | 116 |

| Table 4.10-1 | Page Size of DRAM Connected                                                                             | 127 |

| Table 4.10-2 | Combinations of Bus Widths Available in Areas 4 and 5                                                   | 129 |

| Table 4.15-1 | Mode Setting Using the Combination of Bits (LE2, LE1, and LE0)                                          | 138 |

| Table 4.16-1 | Relationship between Data Bus Widths and Control Signals                                                | 140 |

| Table 4.16-2 | Functions and Bus Widths of DRAM Control Pins                                                           | 155 |

| Table 4.16-3 | Page Size Select Bits                                                                                   | 156 |

| Table 5.4-1  | External Bus Functions to be Selected (1/4)                                                             | 205 |

| Table 5.4-2  | External Bus Functions to be Selected (2/4)                                                             | 206 |

| Table 5.4-3  | External Bus Functions to be Selected (3/4)                                                             | 207 |

| Table 5.4-4  | External Bus Functions to be Selected (4/4)                                                             | 209 |

| Table 6.4-1  | External Interrupt Request Mode                                                                         | 215 |

| Table 8.3-1   | Correspondences between the Interrupt Level Setting Bits and Interrupt Levels       | 229 |

|---------------|-------------------------------------------------------------------------------------|-----|

| Table 8.5-1   | Relationships among Interrupt Causes, Numbers, and Levels (1/2)                     | 231 |

| Table 8.5-2   | Relationships among Interrupt Causes, Numbers, and Levels (2/2)                     | 232 |

| Table 8.7-1   | Settings for the Interrupt Levels for which a Hold Request Cancel Request is Issued | 235 |

| Table 10.2-1  | Selection of UART Operation Modes                                                   | 248 |

| Table 10.6-1  | UART Operation Modes                                                                | 255 |

| Table 10.11-1 | Baud Rates and U-TIMER Reload Values in Asynchronous (Start-Stop) Mode              | 265 |

| Table 10.11-2 | Baud Rates and U-TIMER Reload Values in CLK Synchronous Mode                        | 265 |

| Table 11.2-1  | Selecting the Causes for Starting the A/D Converter                                 | 271 |

| Table 11.2-2  | Selecting the A/D Converter Operation Mode                                          | 272 |

| Table 11.2-3  | Setting the A/D Conversion Start Channel                                            | 273 |

| Table 11.2-4  | Setting the A/D Conversion End Channel                                              | 273 |

| Table 12.2-1  | CSL Bit Setting Clock Source                                                        | 284 |

| Table 13.3-1  | Bit Positions and Returned Values (Decimal)                                         | 296 |

| Table 14.3-1  | Selection of the Count Clock                                                        | 305 |

| Table 14.3-2  | PWM Output When "1" is Written to PGMS                                              | 305 |

| Table 14.3-3  | Selection of Trigger Input Edge                                                     | 305 |

| Table 14.3-4  | Selection of Interrupt Causes                                                       | 306 |

| Table 14.3-5  | Specification of the Polarity of the PWM Output and the Edge                        | 306 |

| Table 14.7-1  | Selection of Ch3 Trigger Input                                                      | 312 |

| Table 14.7-2  | Selection of Ch2 Trigger Input                                                      | 312 |

| Table 14.7-3  | Selection of Ch1 Trigger Input                                                      | 313 |

| Table 14.7-4  | Selection of Ch0 Trigger Input                                                      | 313 |

| Table 15.2-1  | Channel Descriptor Addresses                                                        | 326 |

| Table 15.4-1  | Selection of Transfer Input Detection Levels                                        | 330 |

| Table 15.4-2  | Specification of Transfer Request Acknowledgment Output                             | 330 |

| Table 15.4-3  | Specification of Transfer End Output                                                | 331 |

| Table 15.5-1  | Specification of Transfer Source or Destination Address Update Modes                | 333 |

| Table 15.5-2  | Address Increment/Decrement Unit                                                    | 333 |

| Table 15.5-3  | Specification of Transfer Data Size                                                 | 333 |

| Table 15.5-4  | Transfer Mode Specification                                                         | 334 |

| Table 15.9-1  | Codes Used in the Timing Charts                                                     | 342 |

| Table 16.4-1  | Sector Addresses                                                                    | 358 |

| Table 16.6-1  | Commands                                                                            | 361 |

| Table 16.7-1  | Statuses of the Hardware Sequence Flag                                              | 365 |

| Table A-1     | I/O Map (1/6)                                                                       | 371 |

| Table A-2     | I/O Map (2/6)                                                                       | 372 |

| Table A-3     | I/O Map (3/6)                                                                       | 373 |

|               |                                                                                     |     |

| Table A-4    | I/O Map (4/6)                                                             | 375 |

|--------------|---------------------------------------------------------------------------|-----|

| Table A-5    | I/O Map (5/6)                                                             | 376 |

| Table A-6    | I/O Map                                                                   | 377 |

| Table B-1    | Interrupt Vectors (1/2)                                                   | 379 |

| Table B-2    | Interrupt Vectors (2/2)                                                   | 380 |

| Table C-1    | Explanation of Terms Used in the Pin Status List                          | 383 |

| Table C-2    | Pin Status for 16-bit External Bus Length and 2CA1WR Mode                 | 384 |

| Table C-3    | Pin Status for 16-bit External Bus Length and 2CA1WR Mode                 | 387 |

| Table C-4    | Pin Status in 8-bit External Bus Mode                                     | 390 |

| Table C-5    | Pin Status in Single Chip Mode                                            | 393 |

| Table E-1    | Explanation of Addressing Mode Codes                                      | 405 |

| Table E-2    | Instruction Formats                                                       | 407 |

| Table E.1-1  | Addition and Subtraction Instructions                                     | 410 |

| Table E.1-2  | Compare Operation Instructions                                            | 410 |

| Table E.1-3  | Logical Operation Instructions                                            | 411 |

| Table E.1-4  | Bit Operation Instructions                                                | 411 |

| Table E.1-5  | Multiplication and Division Instructions                                  | 412 |

| Table E.1-6  | Shift Instructions                                                        | 412 |

| Table E.1-7  | Immediate Value Setting or 16/32-Bit Immediate Value Transfer Instruction | 413 |

| Table E.1-8  | Memory Load Instructions                                                  | 413 |

| Table E.1-9  | Memory Store Instructions                                                 | 414 |

| Table E.1-10 | Interregister Transfer Instructions                                       | 414 |

| Table E.1-11 | Standard Branch (Without Delay) Instructions                              | 415 |

| Table E.1-12 | Delayed Branch Instructions                                               | 416 |

| Table E.1-13 | Other Instructions                                                        | 417 |

| Table E.1-14 | 20-Bit Standard Branch Macro Instructions                                 | 418 |

| Table E.1-15 | 20-Bit Delayed-Branch Macro Instructions                                  | 419 |

| Table E.1-16 | 32-Bit Standard Branch Macro Instructions                                 | 420 |

| Table E.1-17 | 32-Bit Delayed-Branch Macro Instructions                                  | 421 |

| Table E.1-18 | Direct Addressing Instructions                                            | 422 |

| Table E.1-19 | Resource Instructions                                                     | 422 |

| Table E.1-20 | Coprocessor Control Instructions                                          | 423 |

## **CHAPTER 1 OVERVIEW**

This chapter provides basic general information on the MB91F109, including its characteristics, block diagram, and function overview.

- 1.1 MB91F109 Characteristics

- 1.2 General Block Diagram of MB91F109

- 1.3 Outside Dimensions

- 1.4 Pin Arrangement Diagrams

- 1.5 Pin Functions

- 1.6 I/O Circuit Format

- 1.7 Memory Address Space

- 1.8 Handling of Devices

#### 1.1 MB91F109 Characteristics

The MB91F109 is a standard single-chip microcontroller using a 32-bit RISC CPU (FR30 series) as its core. It contains various I/O resources and bus control mechanisms for embedded control applications that require high-speed CPU processing.

This microcontroller contains 254-kilobyte flash ROM and 4-kilobyte RAM. It has optimal specifications for embedding applications such as navigation systems, high-performance facsimiles, and printer controls, which require high CPU processing power.

#### ■ Characteristics

#### O FR-CPU

- 32-bit RISC (FR30), load/store architecture, 5-stage pipeline

- Operating frequency: Internal 25 MHz [external 25 MHz] (source oscillation 12.5 MHz with PLL used)

- General-purpose registers: 32 bits x 16

- 16-bit fixed-length instructions (basic instructions), one instruction per cycle

- Inter-memory transfer, bit processing, and barrel shift instructions, which are suitable for embedding applications

- Function entry/exit instructions and register data multiload/store instructions, which are compliant with high-level language instructions

- Register interlock function, which eases assembler coding

- · Branch instruction with delay slot, which reduces overheads in branch processing

- · Built-in adder, supported in the instruction level

- Signed 32-bit addition: 5 cycles

- Signed 16-bit addition: 3 cycles

- Interrupt (PC, PS saving): 6 cycles, 16 priority levels

#### O Bus interface

- Operating frequency: Up to 25 MHz (internal), 25 MHz (external bus)

- 25-bit address bus (32-megabyte address space)

- 16-bit address output, 8-bit or 16-bit data input and output

- Basic bus cycle: 2 clock cycles

- Chip Select output that can be set in 64 kilobytes minimum: 6 lines

- · Interface support for each type of memory

- DRAM interface (areas 4 and 5)

- Automatic wait cycle: Any number of cycles (0 to 7) can be set for each area.

- Unused data and address terminals can be used as I/O ports.

- Support for little endian mode (selecting one of areas 1 to 5)

#### DRAM interface

- 2-bank independent control (areas 4 and 5)

- Double CAS DRAM (normal DRAM interface), single CAS DRAM, and hyper DRAM

- Basic bus cycle: Five cycles in normal mode. Two-cycle access is enabled in high-speed page mode.

- Programmable waveform: Automatic 1-cycle wait can be inserted into RAS or CAS.

- DRAM refresh

- CBR refresh (The interval can be set as desired using the 6-bit timer.)

- · Self-refresh mode

- Support for 8-, 9-, 10-, or 12-line column address

- Choice between 2CAS/1WE and 2WE/1CAS

#### DMAC (DMA controller)

- Eight channels

- Transfer cause: External terminal or internal resource interrupt request

- Transfer sequence

- · Step transfer or block transfer

- · Burst transfer or continuous transfer

- Transfer data length: Selectable from 8, 16, and 32 bits

- A temporary stop is enabled by an NMI/interrupt request.

#### O UART

- Independent three channels

- · Full duplex double buffer

- Data length: 7 to 9 bits (no parity) or 6 to 8 bits (with parity)

- Choice between asynchronous (start-stop synchronization) communication and clock asynchronous communication

- · Multiprocessor mode

- Built-in 16-bit timer (U-Timer) as a baud rate generator, which can generate a desired baud rates

- An external clock can be used as a transfer clock.

- Error detection: Parity error, frame error, and overrun

#### A/D converter (successive approximation conversion type)

- 10-bit resolution, 4 channels

- Successive approximation conversion type: 5.6 µs at 25 MHz

- Built-in sample and hold circuit

- · Conversion mode: Selectable from single conversion, scan conversion, and repeat

#### **CHAPTER 1 OVERVIEW**

conversion

· Starting: Selectable from software, external trigger, and internal timer

#### O Reload timer

• 16-bit timer: Three channels

Internal clock: 2-clock cycle resolution. Selectable from 2-, 8-, and 32-frequency division mode

#### Other interval timers

• 16-bit timer: Three channels (U-Timer)

PWM timer: Four channels

· Watchdog timer: One channel

#### O Bit search module

Searches for the bit position that first changes between 1 and 0 beginning from MSB of a word in one cycle.

#### O Interrupt controller

- External interrupt input: Nonmaskable interrupt, normal interrupt x 4 (INT0 to INT3)

- Internal interrupt causes: UART, DMAC, A/D, reload timer, PWM, UTIMER, and delayed interrupt

- Up to 16 priority levels are programmable for interrupts other than nonmaskable interrupts.

#### O Reset types

· Power-on reset, watchdog timer reset, software reset, and external reset

#### Power save mode

Sleep/stop mode

#### O Clock control

• Gear function: Desired operating clock frequencies can be set for the CPU and peripherals independently.

A gear clock can be selected from 1/1, 1/2, 1/4, and 1/8 (or 1/2, 1/4, 1/8, and 1/16). However, the operating clock frequency for peripherals cannot exceed 25 MHz.

#### O Others

Packages: QFP-100, LQFP-100, FBGA-112

• CMOS technology: 0.5 μm

• Power supply: 3.3 V plus or minus 0.3 V

• 254-kilobyte flash ROM: Can be read, written, and erased by a single power supply.

#### 1.1 MB91F109 Characteristics

### ■ Available Types

|        | MB91V106 | MB91106  | MB91F109  |

|--------|----------|----------|-----------|

| IROM   | -        | 63 Kbyte | -         |

| IRAM   | 64 Kbyte | -        | -         |

| CROM   | -        | 64 Kbyte | 254 Kbyte |

| CRAM   | 64 Kbyte | -        | 2 Kbyte   |

| RAM    | 2 Kbyte  | 2 Kbyte  | 2 Kbyte   |

| I\$    | -        | -        | -         |

| Others | -        | -        | -         |

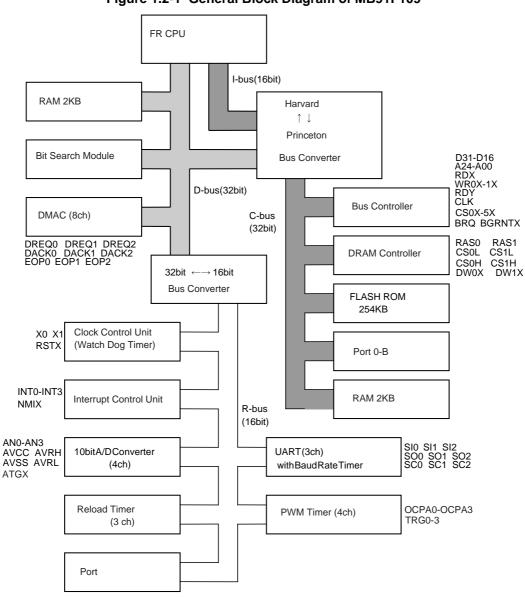

## 1.2 General Block Diagram of MB91F109

#### Figure 1.2.1 is a general MB91F109 block diagram.

#### ■ General Block Diagram of MB91F109

Figure 1.2-1 General Block Diagram of MB91F109

#### Notes:

- Terminals are represented by the function (some terminals are actually multiplexed).

- When REALOS is used, perform time management using an external interrupt or internal timer.

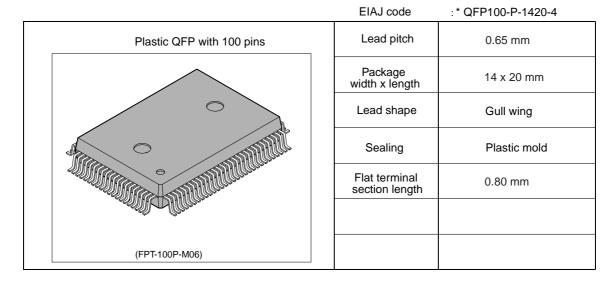

#### 1.3 Outside Dimensions

### Figures 1.3.1 to 1.3.3 show the outside dimensions of the MB91F109.

#### ■ Outside Dimensions (QFP-100)

Figure 1.3-1 Outside Dimensions of FPT-100P-M06

#### **CHAPTER 1 OVERVIEW**

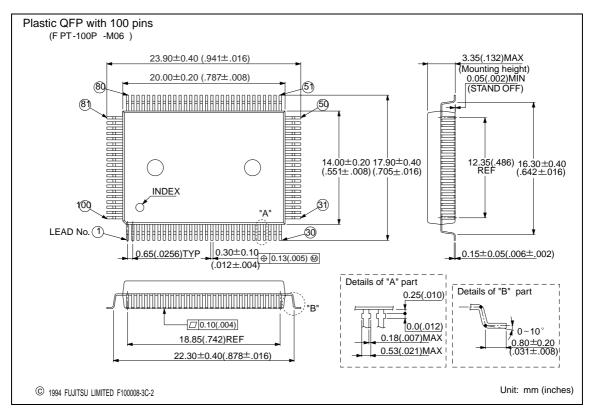

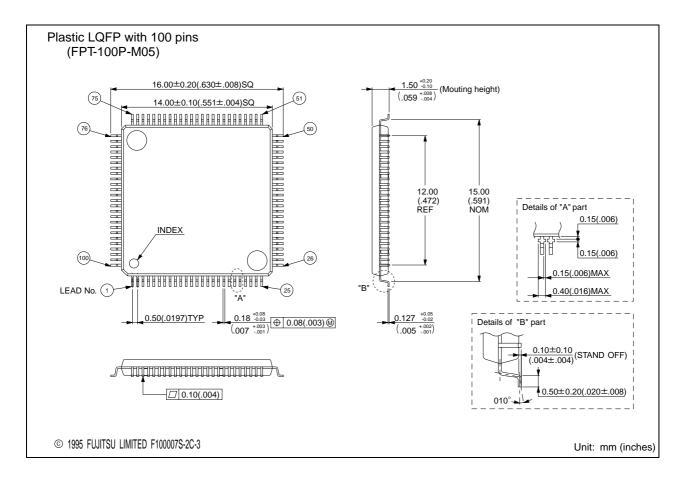

#### ■ Outside Dimensions (LQFP-100)

Figure 1.3-2 Outside Dimensions of FPT-100P-M05

EIAJ code: \*QFP100-P-1414-1

| Plastic LQFP with 100 pins | Lead pitch                | 0.50 mm      |

|----------------------------|---------------------------|--------------|

|                            | Package<br>width x length | 14 x 14 mm   |

|                            | Lead shape                | Gull wing    |

|                            | Sealing                   | Plastic mold |

|                            |                           |              |

|                            |                           |              |

| (FPT-100P-M05)             |                           |              |

#### ■ Outside Dimensions (FBGA-112)

Figure 1.3-3 Outside Dimensions of BGA-112P-M01

## 1.4 Pin Arrangement Diagrams

#### Figures 1.4.1 to 1.4.3 show the pin arrangements of the MB91F109.

■ Pin Arrangements (QFP-100)

Figure 1.4-1 QFP-100 Pin Arrangements DACK0/PE6 DACK1/PE7 PF7/OCPA0/ATGX SO2/PF6/OCPA2 X0 X1 VSS INT2/PE2/SC1 INT3/PE3/SC2 DREQ1/PE5 DREQ0/PE4 CSOL/PB1 RASO/PB0 INTO/PE0 INT1/PE1  $\begin{smallmatrix} 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.0 \\ 0.$ PB2/CS0H SO0/PF1/TRG1 80 PB3/DW0X 2 79 SI0/PF0/TRG0 EOP2/PB4/RAS1 3 AN3 78 DREQ2/PB5/CS1L 4 77 AN2 DACK2/PB6/CS1H 5 AN1 76 PB7/DW1X 6 75 AN0 VCC AVSS/AVRL 7 74 PA6/CLK **AVRH** 8 73 PA5/CS5X **AVCC** 72 A24/EOP0/P70 PA4/CS4X 10 71 EOP1/PA3/CS3X 70 11 A23/P67 MB91F109 PA2/CS2X 12 A22/P66 69 PA1/CS1X 13 68 VSS PA0/CS0X 14 A21/P65 67 **NMIX** 15 A20/P64 66 (TOP VIEW) VCC 16 65 A19/P63 **RSTX** 17 64 A18/P62 VSS 18 63 A17/P61 FPT-100P-M06 MD0 19 62 A16/P60 20 MD1 61 A15/P57 21 60 MD2 A14/P56 59 22 P80/RDY A13/P55 23 58 P81/BGRNTX A12/P54 24 57 P82/BRQ A11/P53 25 56 P83/RDX A10/P52 55 26 P84/WR0X A09/P51 27 54 P85/WR1X A08/P50 53 28 P20/D16 A07/P47 29 52 P21/D17 A06/P46 30 51 P22/D18 ■ A05/P45 P26/D22 P27/D23 P30/D24 P31/D25 P32/D26 P34/D28 P36/D29 P36/D30 VSS P37/D31 P40/A00

10

#### ■ Pin Arrangements (LQFP-100)

Figure 1.4-2 LQFP-100 Pin Arrangements RAS1/PB4/EOP2

DW/0X/PB3

CS0L/PB1

RAS0/PB0

INT0/PE0

INT1/PE1

VCC

X0

X1

VSS

INT2/PE2/SC1

INT3/PE3/SC2

DREQ0/PE4

DREQ1/PE5

DACK0/PE6

DACK1/PE7

PF7/OCPA0/ATGX

SO2/PF5/OCPA1

SO1/PF4/TRG3

SI1/PF3/TRG2

SC0/PF3/OCPA3 AN3 DREQ2/PB5/CS1L 1 2 3 4 5 74 AN2 DACK2/PB6/CS1H 73 72 PB7/DW1X AN1 AN0 VCC 71 70 PA6/CLK PA5/CS5X PA4/CS4X EOP1/PA3/CS3X AVSS/AVRL 6 7 **AVRH** 69 **AVCC** A24/EOP0/P70 8 68 67 A23/P67 9 PA2/CS2X 66 PA1/CS1X PA0/CS0X 10 A22/P66 MB91F109 65 **VSS** 11 A21/P65 A20/P64 12 13 64 NMIX 63 62 VCC (TOP VIEW) RSTX VSS 14 A19/P63 15 61 A18/P62 60 59 58 57 56 55 54 A17/P61 MD0 16 FPT-100P-M05 17 A16/P60 MD1 18 A15/P57 MD2 19 A14/P56 P80/RDY 20 A13/P55 P81/BGRNTX 21 A12/P54 P82/BRQ 22 A11/P53 P83/RDX 23 24 25 53 52 A10/P52 P84/WR0X A09/P51 P85/WR1X 51 A08/P50 P20/D16  $\begin{array}{c} 222 \\ 222 \\ 222 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\ 232 \\$ P21/D17

P22/D18

P22/D18

P22/D18

P24/D20

P26/D22

P26/D22

P27/D26

P37/D26

P37/D31

P40/A00

P44/A04

P44/A04

P45/A07

P46/A06

11

#### **CHAPTER 1 OVERVIEW**

#### ■ Pin Arrangements (FBGA-112)

11 10 9 8 7 TOP VIEW 6 5 4 3 2 1 INDEX В С D Ε F G L

Figure 1.4-3 FBGA-112 Pin Arrangements

Table 1.4.1 shows the cross-references of the FBGA package pin names.

Table 1.4-1 FBGA Package Pin Names

| BALL-No.       | PIN-NAME                                  | BALL-No.       | PIN-NAME                     | BALL-No. | PIN-NAME  |

|----------------|-------------------------------------------|----------------|------------------------------|----------|-----------|

| A1             | N.C                                       | D6             | VCC                          | H9       | A14/ P56  |

| A2             | RAS1/ PB4/ EOP2                           | D7             | DREQ0/ PE4                   | H10      | A13/ P55  |

| A3             | CS0L/ PB1                                 | D8             | OCPA0/ PF7/ ATGX             | H11      | N.C.      |

| A4             | INT1/ PE1                                 | D9             | AN2                          | J1       | RDX/ P83  |

| A5             | X1                                        | D10            | AVRH                         | J2       | WR0X/ P84 |

| A6             | INT3/ SC2/ PE3                            | D11            | AVCC                         | J3       | D21/ P25  |

| A7             | DACK1/ PE7                                | E1             | CS1X/ PA1                    | J4       | D24/ P30  |

| A8             | SI2/ OCPA1/ PF5                           | E2             | CS0X/ PA0                    | J5       | N.C.      |

| A9             | SC0/ OCPA3/ PF2                           | E3             | NMIX                         | J6       | VSS       |

| A10            | SI0/ TRG0/ PF0                            | E4             | VCC                          | J7       | VCC       |

| A11            | N.C.                                      | E8             | AVSS/ AVRL                   | J8       | A06/ P46  |

| B1             | CS1L/ PB5/ DREQ2                          | E9             | N.C.                         | J9       | A12/ P54  |

| B2             | CS1H/ PB6/ DACK2                          | E10            | A23/ P67                     | J10      | A11/ P53  |

| B3             | CS0H/ PB2                                 | E11            | A22/ P66                     | J11      | N.C.      |

| B4             | INT0/ PE0                                 | F1             | RSTX                         | K1       | D16/ P20  |

| B5             | X0                                        | F2             | VSS                          | K2       | D18/ P22  |

| B6             | INT2/ SC1/ PE2                            | F3             | MD0                          | K3       | D20/ P24  |

| B7             | DACK0/ PE6                                | F4             | MD2                          | K4       | D23/ P27  |